**am**  **AS1181**

# Datasheet

**Published by ams-OSRAM AG**

Tobelbader Strasse 30, 8141 Premstaetten, Austria

Phone +43 3136 500-0

[ams-osram.com](http://ams-osram.com)

© All rights reserved

**am**  **OSRAM**

# Table of contents

|           |                                                              |           |

|-----------|--------------------------------------------------------------|-----------|

| <b>1</b>  | <b>General description .....</b>                             | <b>3</b>  |

| 1.1       | Key benefits & features.....                                 | 4         |

| 1.2       | Applications .....                                           | 4         |

| 1.3       | Block diagram .....                                          | 5         |

| <b>2</b>  | <b>Ordering information .....</b>                            | <b>6</b>  |

| <b>3</b>  | <b>Pin assignment .....</b>                                  | <b>7</b>  |

| 3.1       | Pin diagram.....                                             | 7         |

| 3.2       | Pin description .....                                        | 8         |

| <b>4</b>  | <b>Absolute maximum ratings .....</b>                        | <b>9</b>  |

| <b>5</b>  | <b>Electrical characteristics.....</b>                       | <b>10</b> |

| <b>6</b>  | <b>Typical operating characteristics .....</b>               | <b>12</b> |

| <b>7</b>  | <b>Functional description.....</b>                           | <b>18</b> |

| 7.1       | Operation modes .....                                        | 18        |

| 7.2       | Safety monitors .....                                        | 29        |

| 7.3       | Interrupt controller.....                                    | 33        |

| 7.4       | Serial interface description (I <sup>2</sup> C and I3C)..... | 37        |

| <b>8</b>  | <b>Register description .....</b>                            | <b>41</b> |

| 8.1       | Detailed register description .....                          | 41        |

| <b>9</b>  | <b>Application information.....</b>                          | <b>77</b> |

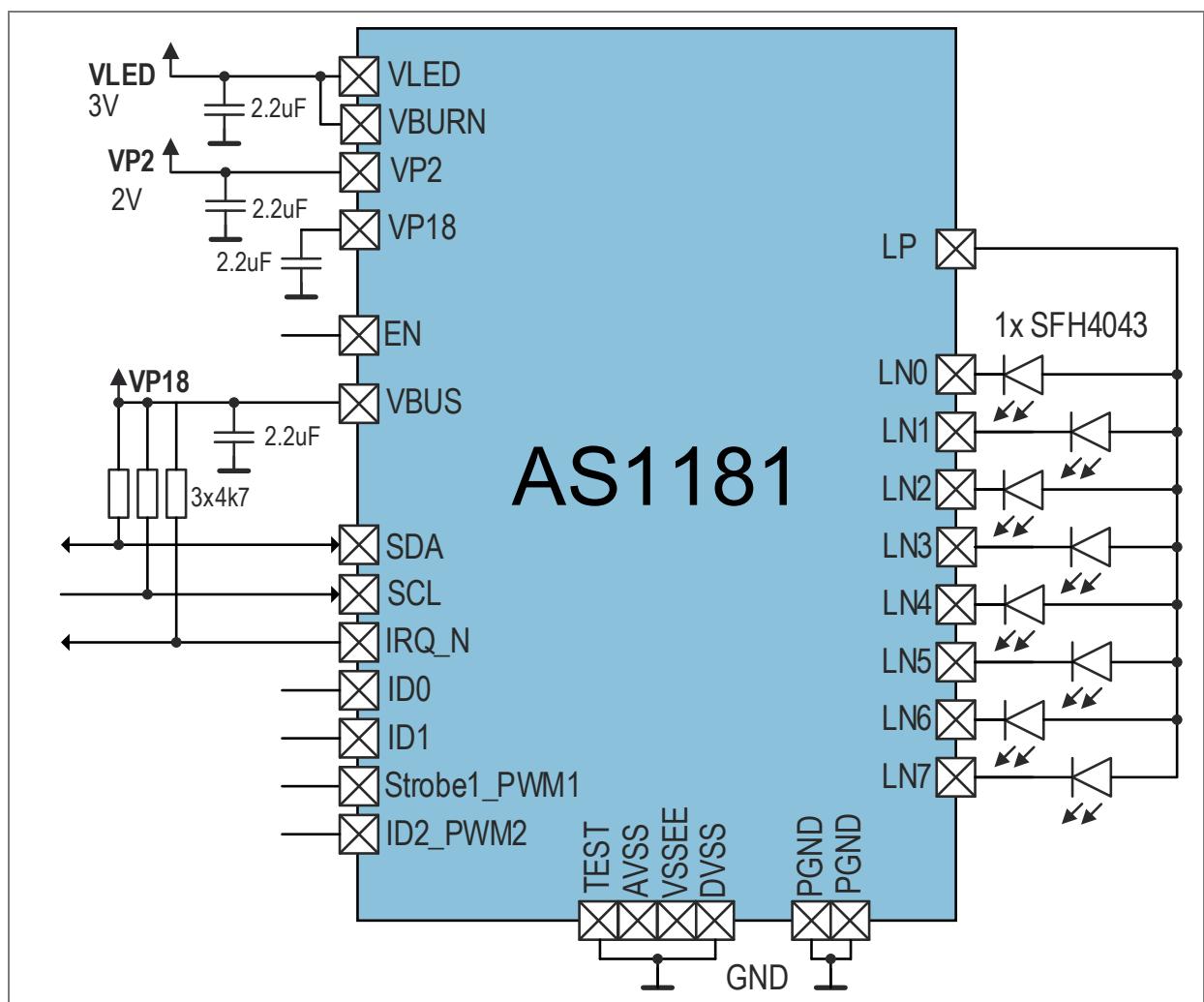

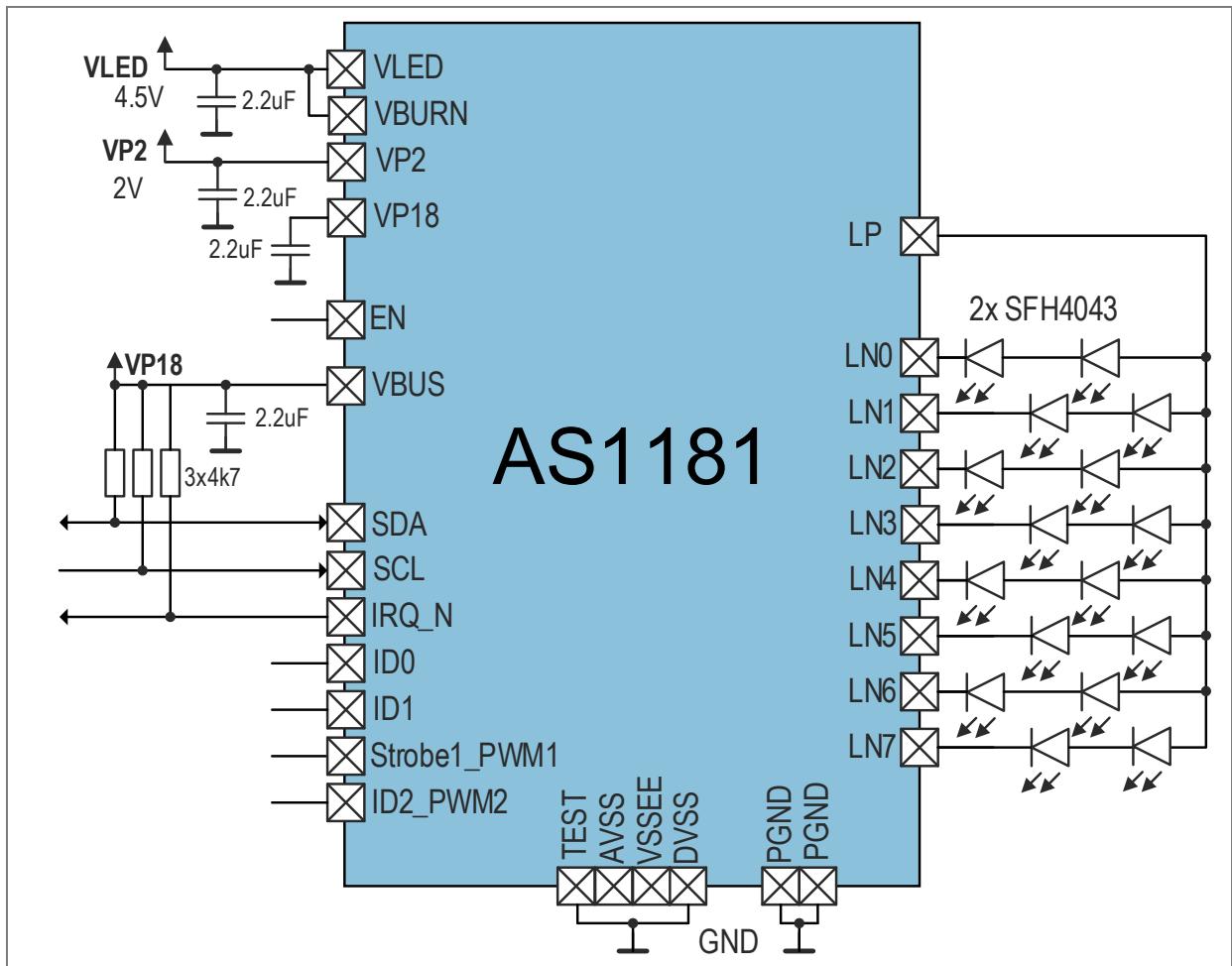

| 9.1       | Schematic .....                                              | 77        |

| <b>10</b> | <b>Package drawings &amp; markings .....</b>                 | <b>79</b> |

| <b>11</b> | <b>Revision information .....</b>                            | <b>81</b> |

| <b>12</b> | <b>Legal information .....</b>                               | <b>82</b> |

# AS1181 8-channel LED/VCSEL driver with enhanced safety features

## 1 General description

AS1181 is an 8-channel highly integrated self-contained LED/VCSEL driver for near to eye applications such as Augmented Reality (AR) and Virtual Reality (VR) glasses. The device integrates extended safety monitoring functions to ensure eye safe operation. These safety monitors include LED short detection, LED open detection, LED overcurrent protection, LED on time monitor as well as temperature shutdown and a built-in-self test (BIST).

The device is configurable via a serial wire interface (I<sup>2</sup>C or I3C) with interrupt and provides two Strobe/PWM inputs to synchronize illumination with up to two external cameras for binocular eye tracking systems.

The LED current is individually programmable per channel, and it can drive up to 2 IR LEDs per current sink with a minimum ON time of 10µs and a maximum current of 66mA per channel.

General purpose LED driving applications can be supported via a direct PWM input applied at the Strobe pin and it can drive RGB or white LEDs considering a maximum forward voltage of 5V.

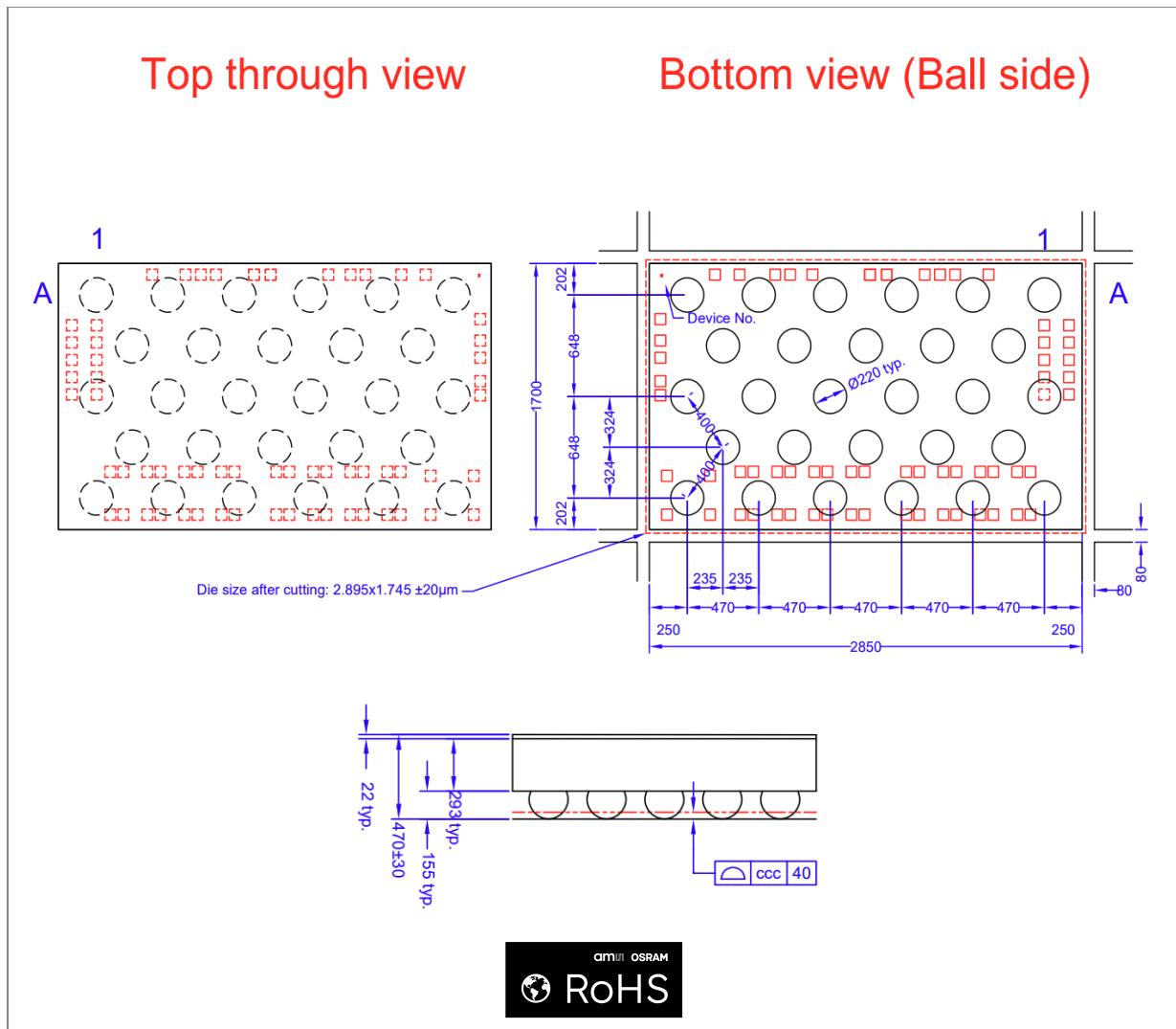

The device comes in a tiny wafer-level-chip-scale package (WLCSP) with 0.4mm pitch and dimensions of 2.9mm x 1.75mm x 0.5mm (L x W x H).

## 1.1 Key benefits & features

The benefits and features of AS1181, 8-channel LED/VCSEL driver with enhanced safety features are listed below:

Table 1: Added value of using AS1181

| Benefits                                                                                                                                              | Features                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fully self-contained fault detection and protection enables easier implementation of eye safety functionality in end devices over discrete solutions. | Enhanced safety monitors: <ul style="list-style-type: none"><li>• High side over current detection (Anode)</li><li>• High side LP node short detection (Anode)</li><li>• Low side open/short LED detection (Cathode)</li><li>• Built-in-self test (BIST)</li><li>• Illumination time monitor</li><li>• Over &amp; low temperature shutdown</li></ul> |

| Easy integration into size constraint applications                                                                                                    | Tiny WL-CSP 28 package with 0.4mm pitch.<br>2.9mm x 1.75mm x 0.5mm (L x W x H)                                                                                                                                                                                                                                                                       |

| Support for binocular eye tracking systems                                                                                                            | Dual trigger input to start and synchronize illumination with two eye tracking cameras.                                                                                                                                                                                                                                                              |

## 1.2 Applications

- Eye- / face / hand tracking in AR/VR and XR glasses

- Iris recognition

- General purpose LED driver with enhanced safety features

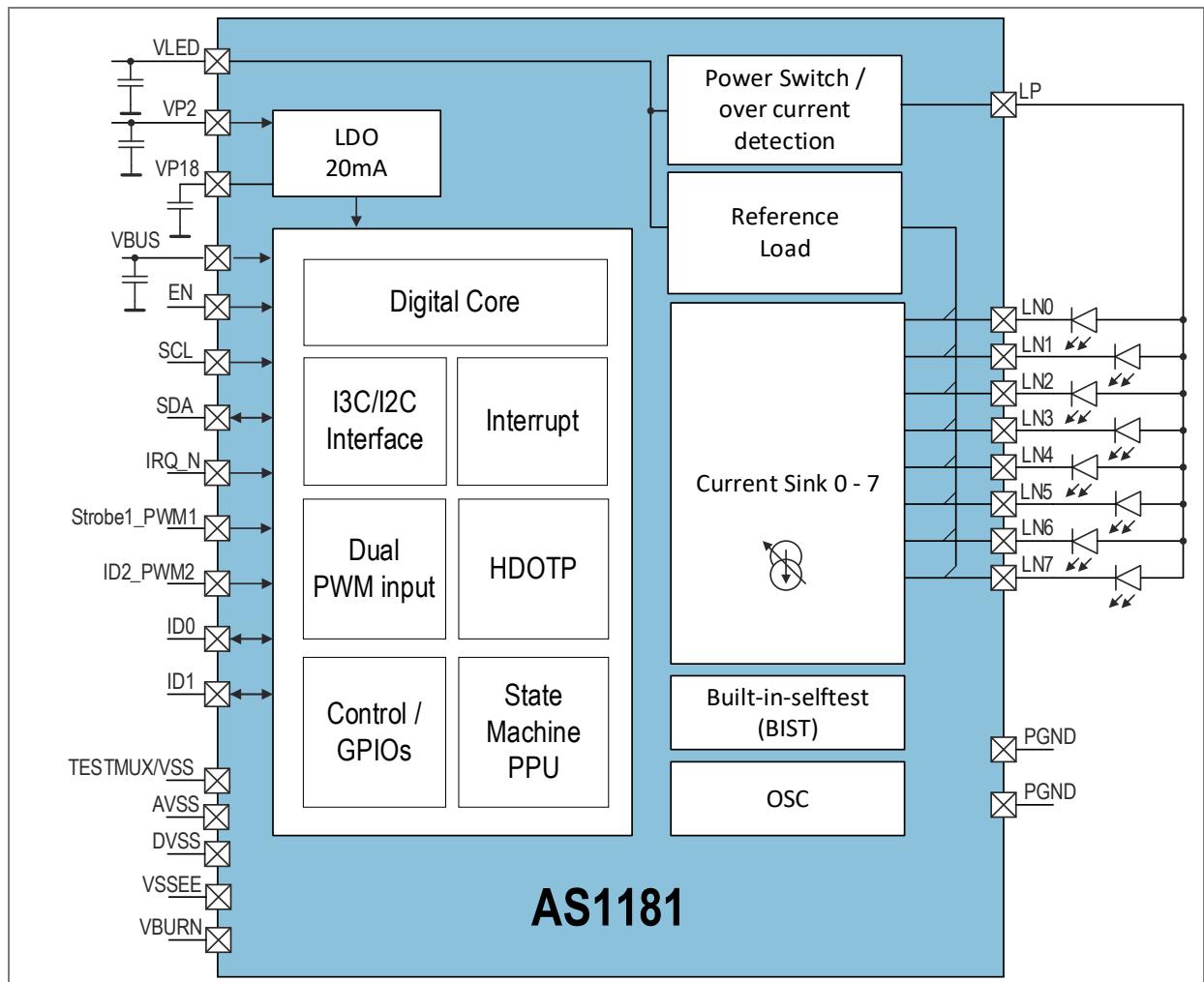

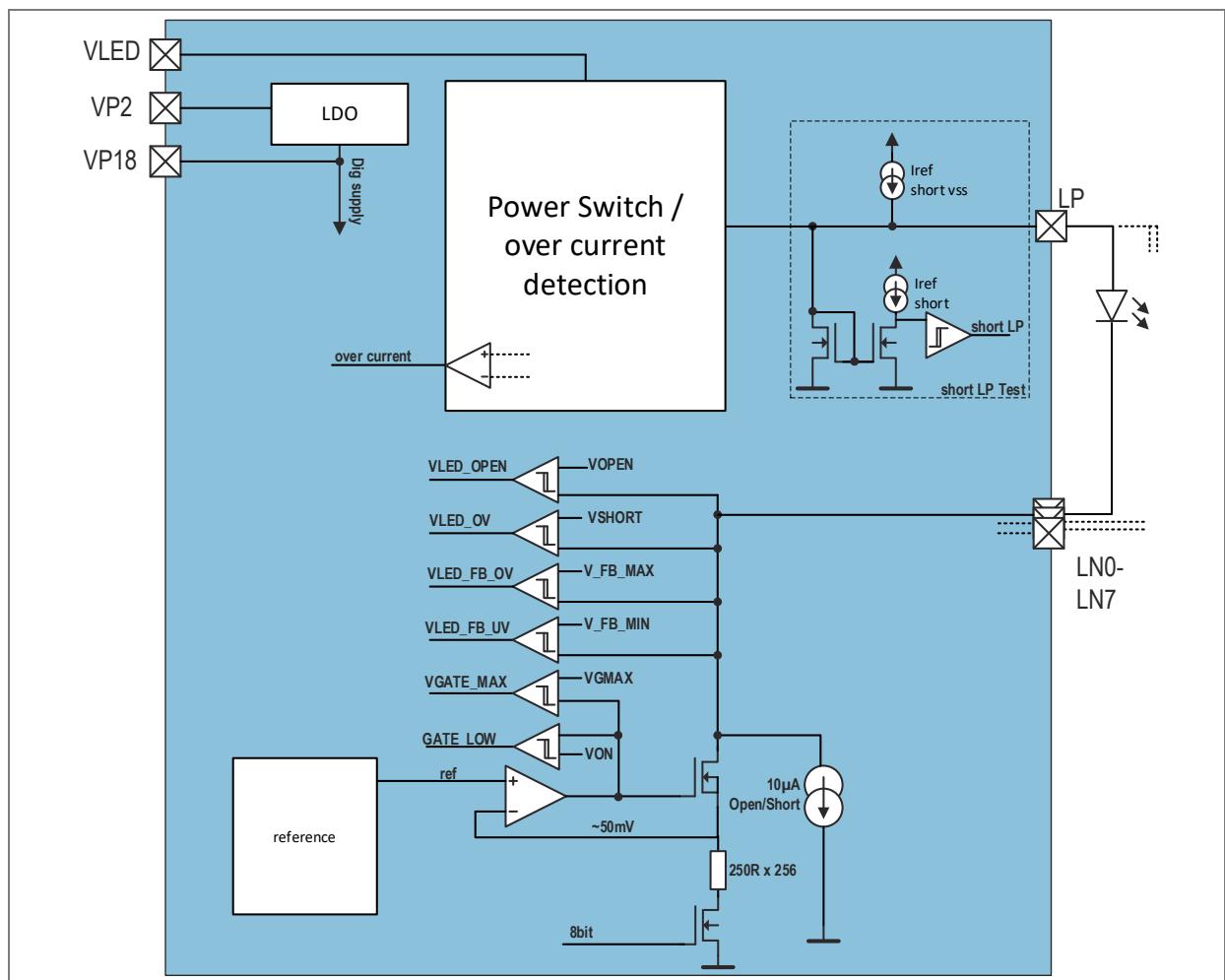

## 1.3 Block diagram

The functional blocks of this device are shown below:

Figure 1: Functional blocks of AS1181

## 2 Ordering information

| Ordering code | Package  | Product type/Marking | Delivery form | Delivery quantity |

|---------------|----------|----------------------|---------------|-------------------|

| Q65113A9356   | WLCSP-28 | AS1181               | Tape & reel   | 1000 pcs/reel     |

| Q65115A2377   | WLCSP-28 | AS1181               | Tape & reel   | 4000 pcs/reel     |

## 3 Pin assignment

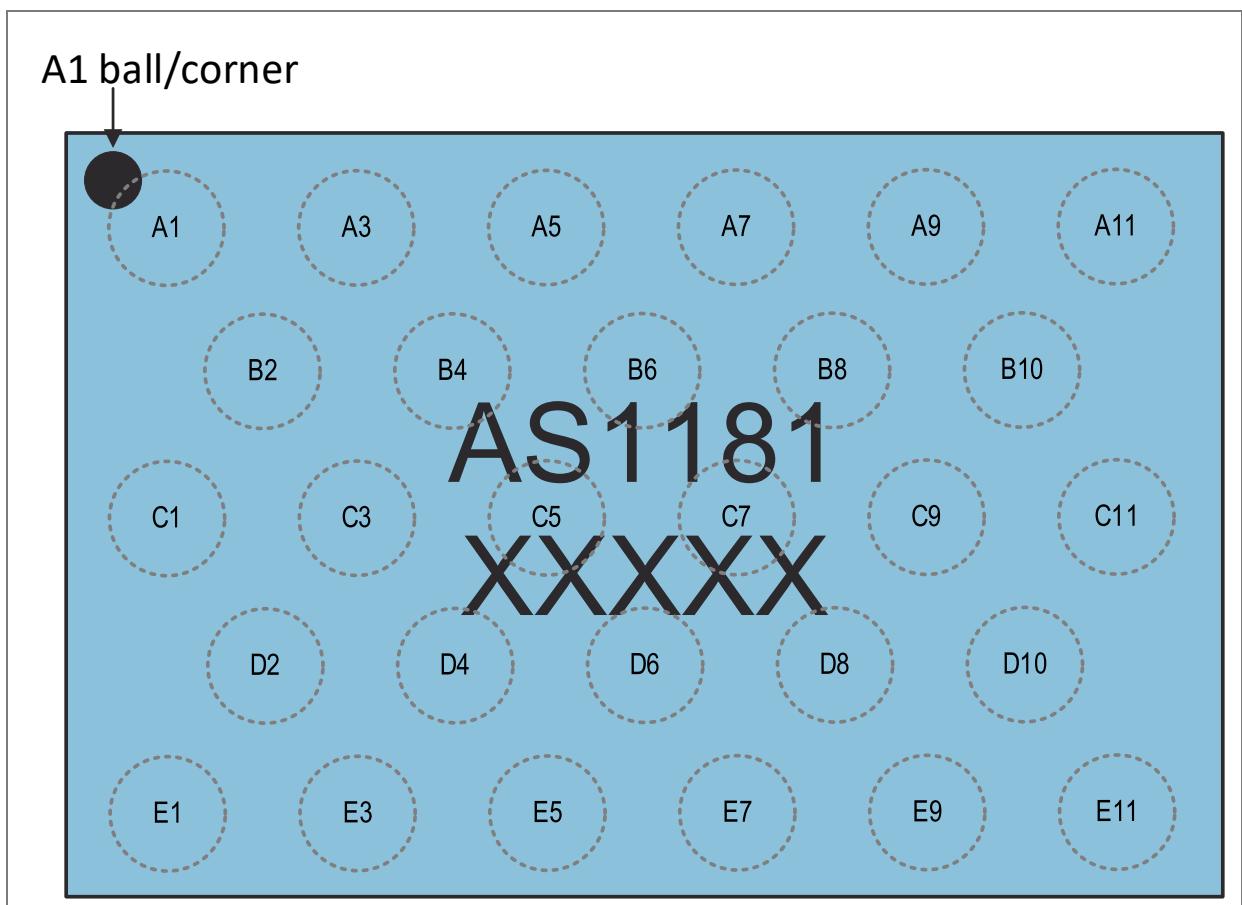

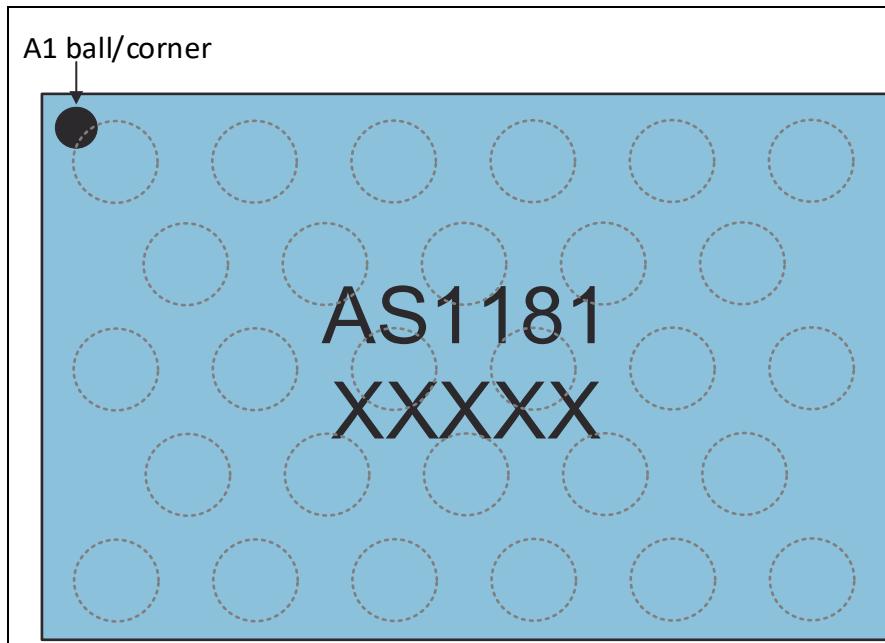

### 3.1 Pin diagram

Figure 2: Pin diagram of AS1181

## 3.2 Pin description

Table 2: Pin description of AS1181

| Pin number | Pin name     | Pin type <sup>(1)</sup> | Description                                                           |

|------------|--------------|-------------------------|-----------------------------------------------------------------------|

| A1         | LP           | AIO                     | Anode LED connection (High Side Current Monitor Output)               |

| A3         | VSS_EE       | PWR                     | Connect to ground                                                     |

| A5         | SCL          | DI                      | I <sup>2</sup> C / I3C clock                                          |

| A7         | ID2_PWM2     | DI                      | ID2 pin or / PWM2 input                                               |

| A9         | IRQ_N        | DO                      | Interrupt output                                                      |

| A11        | STROBE1_PWM1 | DI                      | STROBE input or / PWM1 input                                          |

| B2         | VBURN        | PWR                     | HDOTP burn supply / Connect to VLED in normal application             |

| B4         | VBUS         | PWR                     | Digital supply voltage / interface voltage. For 1.8V connect to VP18. |

| B6         | SDA          | DIO                     | I <sup>2</sup> C / I3C data                                           |

| B8         | ID0          | DIO                     | I <sup>2</sup> C address pin / GPIO                                   |

| B10        | DVSS         | PWR                     | Connect to ground                                                     |

| C1         | VLED         | PWR                     | LED supply voltage                                                    |

| C3         | EN           | DIO                     | Enable input pin                                                      |

| C5         | TEST         | DIO                     | Test enable pin / connect to ground                                   |

| C7         | PVSS         | PWR                     | Power ground / connect to ground                                      |

| C9         | ID1          | DIO                     | I <sup>2</sup> C address pin / GPIO                                   |

| C11        | AVSS         | PWR                     | Analog ground / connect to ground                                     |

| D2         | LN7          | AIO                     | Current sink input 7 (LED cathode)                                    |

| D4         | LN5          | AIO                     | Current sink input 5 (LED cathode)                                    |

| D6         | LN3          | AIO                     | Current sink input 3 (LED cathode)                                    |

| D8         | LN1          | AIO                     | Current sink input 1 (LED cathode)                                    |

| D10        | VP18         | PWR                     | LDO output. Connect 2.2 $\mu$ F capacitor close to pin VP18.          |

| E1         | PVSS         | PWR                     | Power ground / connect to ground                                      |

| E3         | LN6          | AIO                     | Current sink input 6 (LED cathode)                                    |

| E5         | LN4          | AIO                     | Current sink input 4 (LED cathode)                                    |

| E7         | LN2          | AIO                     | Current sink input 2 (LED cathode)                                    |

| E9         | LN0          | AIO                     | Current sink input 0 (LED cathode)                                    |

| E11        | VP2          | PWR                     | LDO Input. Connect 2.2 $\mu$ F capacitor close to pin VP2.            |

(1) PWR Power Pin

AIO Analog Input & Output

DIO Digital Input & Output

DI Digital Input

DO Digital Output

## 4 Absolute maximum ratings

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under “Operating Conditions” is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3: Absolute maximum ratings of AS1181

| Symbol                                           | Parameter                          | Min        | Max | Unit                     | Comments                           |

|--------------------------------------------------|------------------------------------|------------|-----|--------------------------|------------------------------------|

| <b>Electrical parameters</b>                     |                                    |            |     |                          |                                    |

| $V_{LED}$                                        | LED supply voltage to ground       | -0.3       | 5.5 | V                        | Referenced to GND                  |

| $V_{P2}$                                         | LDI supply voltage input           | -0.3       | 5.5 | V                        | Referenced to GND                  |

| $V_{BURN}$                                       | VBURN voltage to ground            | -0.3       | 6.5 | V                        | Referenced to GND                  |

| $I_{SCR}$                                        | Input current (latch-up immunity)  | $\pm 100$  |     | mA                       | JEDEC JESD78E                      |

| <b>Electrostatic discharge</b>                   |                                    |            |     |                          |                                    |

| $ESD_{HBM}$                                      | Electrostatic discharge HBM        | $\pm 2000$ |     | V                        | JS-001-2017                        |

| $ESD_{CDM}$                                      | Electrostatic discharge CDM        | $\pm 500$  |     | V                        | JS-002-2018                        |

| <b>Temperature ranges and storage conditions</b> |                                    |            |     |                          |                                    |

| $T_A$                                            | Ambient temperature                | -20        | 125 | °C                       |                                    |

| $T_{STRG}$                                       | Storage temperature range          | -40        | 85  | °C                       |                                    |

| $T_{BODY}$                                       | Package body temperature           | 260        |     | °C                       | IPC/JEDEC J-STD-020 <sup>(1)</sup> |

| $RH_{NC}$                                        | Relative humidity (non-condensing) | 5          | 85  | %                        |                                    |

| <b>MSL</b>                                       | Moisture sensitivity level         | 1          |     | Floor lifetime unlimited |                                    |

(1) The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 “Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices.” The lead finish for Pb-free leaded packages is “Matte Tin” (100 % Sn).

## 5 Electrical characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Table 4: Electrical characteristics of AS1181

| Symbol                             | Parameter                                               | Min  | Typ | Max  | Unit | Comment                                                                        |

|------------------------------------|---------------------------------------------------------|------|-----|------|------|--------------------------------------------------------------------------------|

| <b>Operating conditions</b>        |                                                         |      |     |      |      |                                                                                |

| $T_{A\_OP}$                        | Ambient temperature operating                           | -20  | 25  | 85   | °C   | In this range all specified parameters are met                                 |

| <b>Power supplies and GND</b>      |                                                         |      |     |      |      |                                                                                |

| $V_{LED}$                          | LED supply voltage                                      | 2.6  |     | 5.5  | V    |                                                                                |

| $V_{P2}$                           | Supply voltage for LDO                                  | 2.0  | 2.1 | 5.5  | V    | If only one supply voltage is available $V_{LED}$ can be connected to $V_{P2}$ |

| $V_{P18}$                          | Output voltage of LDO                                   | 1.71 | 1.8 | 1.89 | V    | Supply for analog and digital circuits                                         |

| $V_{BUS}$                          | Supply voltage VBUS                                     | 1.08 | 1.2 | 1.98 | V    | Interface voltage. For 1.8V connect to VP18.                                   |

| $I_{SHUTDOWN}$                     | Shutdown current when EN = 0                            |      |     | 1    | µA   |                                                                                |

| $P_{SLEEP}$                        | Sleep power consumption                                 | 100  |     | 220  | µW   |                                                                                |

| $P_{IDLE}$                         | Idle power consumption                                  | 1.4  |     | 4    | mW   |                                                                                |

| <b>Current sink specifications</b> |                                                         |      |     |      |      |                                                                                |

| $V_{comp}$                         | Compliance / Headroom voltage of current sinks          |      |     | 0.4  | V    |                                                                                |

| $I_{MATCH}^{(1)}$                  | Matching between current sinks from -10°C to 85°C $T_A$ | -1.5 |     | 1.5  | %    |                                                                                |

| $I_{ACC}^{(2)}$                    | Absolute current sink accuracy full range               | -2.5 |     | 2.5  | %    | Full current and temp range                                                    |

| $I_{RANGE}$                        | Current sink range                                      | 0    |     | 66   | mA   | 250µA LSB                                                                      |

| $I_{RES}$                          | Current sink resolution                                 |      |     | 8    | bit  |                                                                                |

| $T_{ON\_MIN}$                      | Minimum LED on time                                     | 10   |     |      | µs   |                                                                                |

| <b>Temperature monitors</b>        |                                                         |      |     |      |      |                                                                                |

| $TEMP_{OT}$                        | High temperature shutdown                               |      |     | 140  | °C   |                                                                                |

| $TEMP_{UT}$                        | Low temperature shutdown                                | -20  |     |      | °C   |                                                                                |

| Symbol                          | Parameter                       | Min                     | Typ       | Max           | Unit | Comment                                                                                                                     |

|---------------------------------|---------------------------------|-------------------------|-----------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------|

| <b>IO parameters</b>            |                                 |                         |           |               |      |                                                                                                                             |

| $V_{IL}$                        | Digital input low voltage       | 0                       | 0.3x VBUS |               | V    |                                                                                                                             |

| $V_{IH}$                        | Digital input high voltage      | 0.7x VBUS               | 1.98      |               | V    |                                                                                                                             |

| $V_{OL}$                        | Digital output low voltage      | 0                       | 270       | mV            |      | I3C mode; $IOL = 3\text{mA}$                                                                                                |

| $V_{OH}$                        | Digital output high voltage     | VDD-0.27                |           |               | V    | I3C mode; $IOL = 3\text{mA}$                                                                                                |

| $f_{SCL\_I2C}$                  | $I^2\text{C}$ maximum frequency |                         | 1         | MHz           |      |                                                                                                                             |

| $f_{SCL\_I3C}$                  | I3C maximum frequency           |                         | 12.5      | MHz           |      |                                                                                                                             |

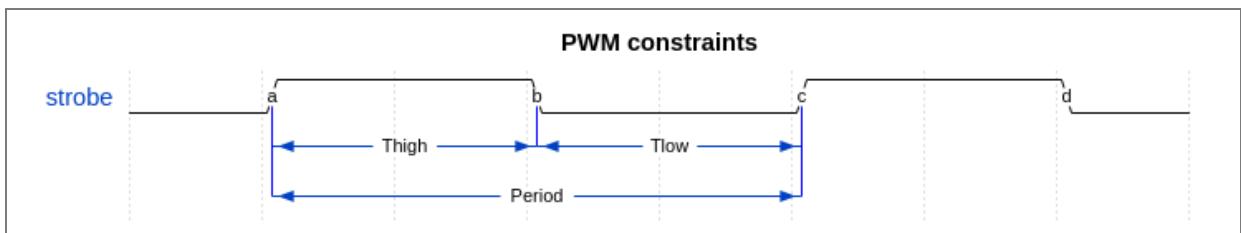

| <b>PWM inputs<sup>(3)</sup></b> |                                 |                         |           |               |      |                                                                                                                             |

| $T_{HIGH}$                      | Strobe/PWM high time            | 20                      | 15000     | $\mu\text{s}$ |      |                                                                                                                             |

| $T_{LOW}$                       | Strobe/PWM low time             | $65+T_{\text{stagger}}$ |           | $\mu\text{s}$ |      | $*T_{\text{stagger}}$ - time needed to perform all the staggering for all groups, if staggering is disabled equals to zero. |

| $P_{PWM}$                       | PWM period                      | 0.2                     | 16.6      | ms            |      | PWM1 and PWM2 shall have the same period in dual PWM input mode.                                                            |

| $f_{PWM}$                       | PWM frequency                   | 60                      | 5000      | Hz            |      |                                                                                                                             |

| DC                              | Duty cycle                      | 10                      | 90        | %             |      |                                                                                                                             |

| $t_{\text{skew}}$               | PWM1&2 input skew               |                         | 10        | $\mu\text{s}$ |      | Maximum skew between PWM1 and PWM2 input in all modes.                                                                      |

- (1) Error/current sink mismatch calculated with all channel currents averaged.

- (2) Calibrated and measured on every device in final test (ATE). System measurement accuracy and solder shift are not included. Accuracy defined on device level.

- (3) Valid in external PWM mode for inputs STROBE1\_PWM1 & ID2\_PWM2

## 6 Typical operating characteristics

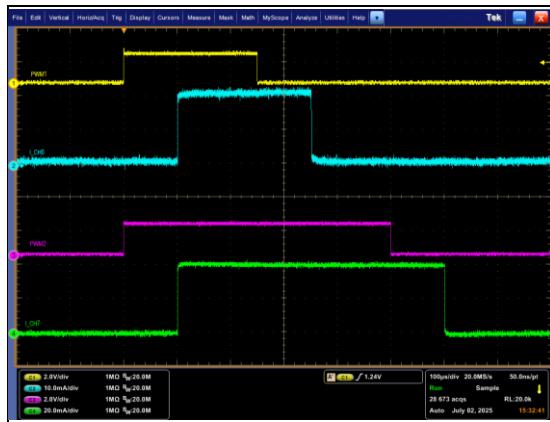

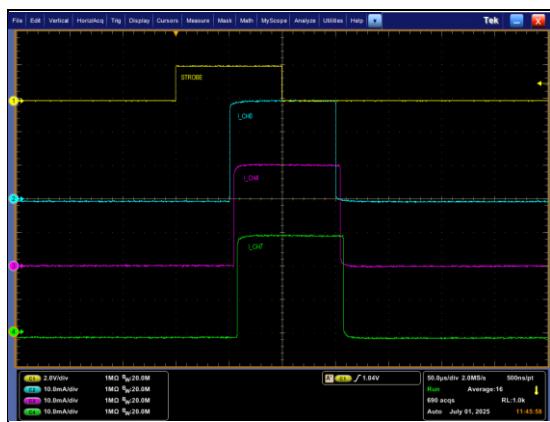

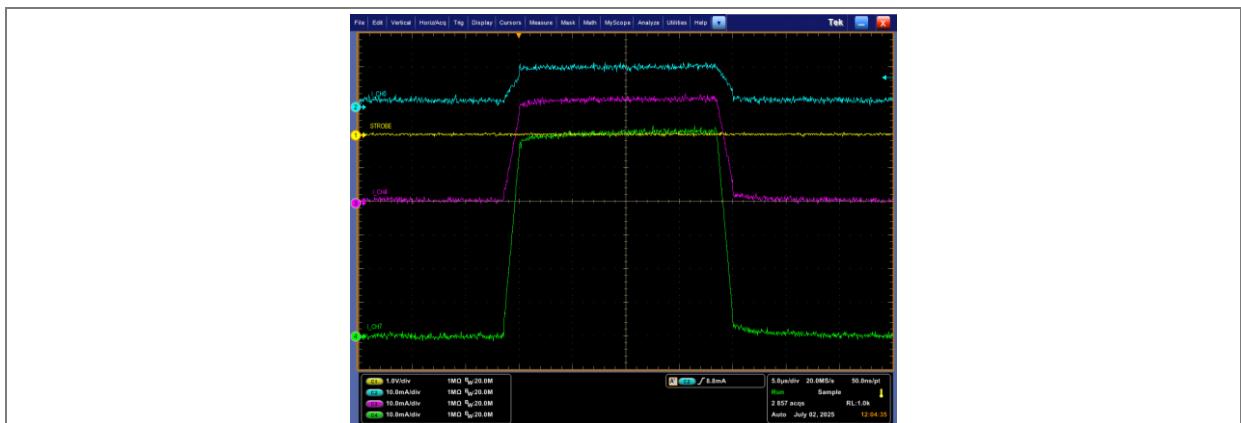

Figure 3: Dual PWM input, T\_STAGGER = 0 $\mu$ s

(1) I\_CH0 = 20mA; I\_CH7 = 40mA

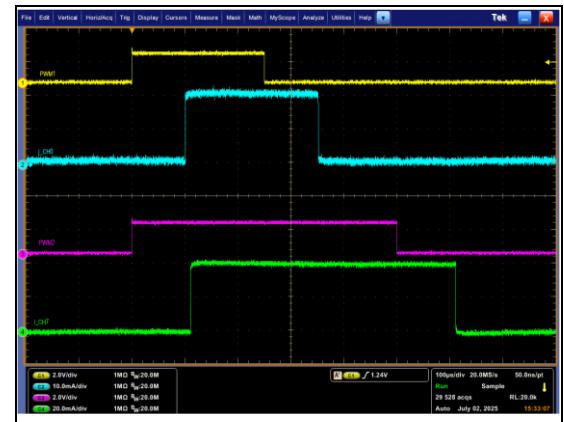

Figure 4: Dual PWM input, T\_STAGGER = 10 $\mu$ s

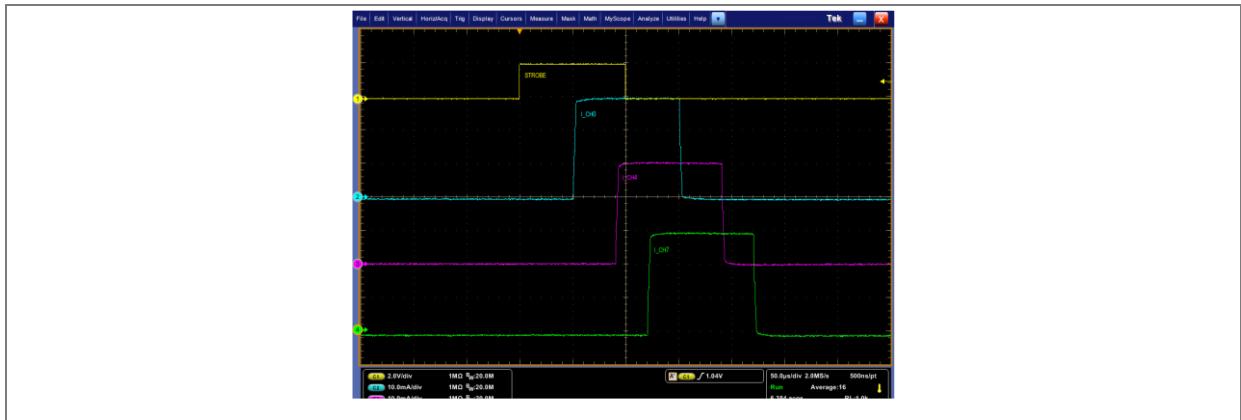

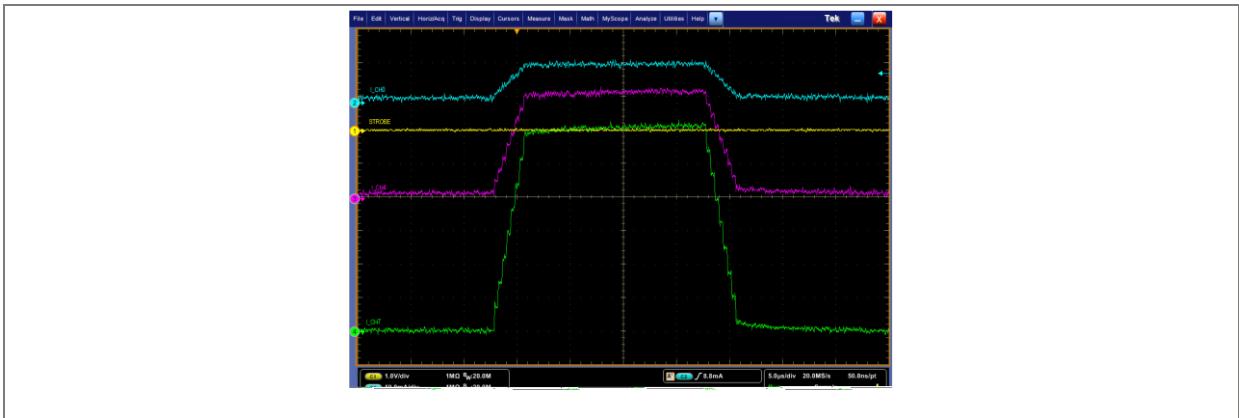

Figure 5: 1 PWM input, T\_STAGGER = 1 $\mu$ s

(1) I\_CH0, I\_CH4, I\_CH7 = 30mA

Figure 6: 1 PWM input, T\_STAGGER = 10 $\mu$ s

Figure 7: 1 PWM input, T\_STAGGER = 1μs

- (1)  $I_{CH0}, I_{CH4}, I_{CH7} = 30\text{mA}$

- (2) Slew rate =  $24 \times 4$

Figure 8: Current pulse 20μs ON time

- (1)  $I_{CH0} = 10\text{mA}, I_{CH4} = 20\text{mA}, I_{CH7} = 60\text{mA}$

- (2) Slew rate = 0x1

Figure 9: Current pulse 20 $\mu$ s ON time

- (1)  $I_{CH0} = 10mA$ ,  $I_{CH4} = 20mA$ ,  $I_{CH7} = 60mA$

- (2) Slew rate = 3x4

Figure 10: Current pulse 20 $\mu$ s ON time

- (1)  $I_{CH0} = 10mA$ ,  $I_{CH4} = 20mA$ ,  $I_{CH7} = 60mA$

- (2) Slew rate = 15 x 6

Figure 11: Current pulse 20 $\mu$ s ON time

- (1)  $I_{CH0} = 10\text{mA}$ ,  $I_{CH4} = 20\text{mA}$ ,  $I_{CH7} = 60\text{mA}$

- (2) Slew rate =  $28 \times 8$

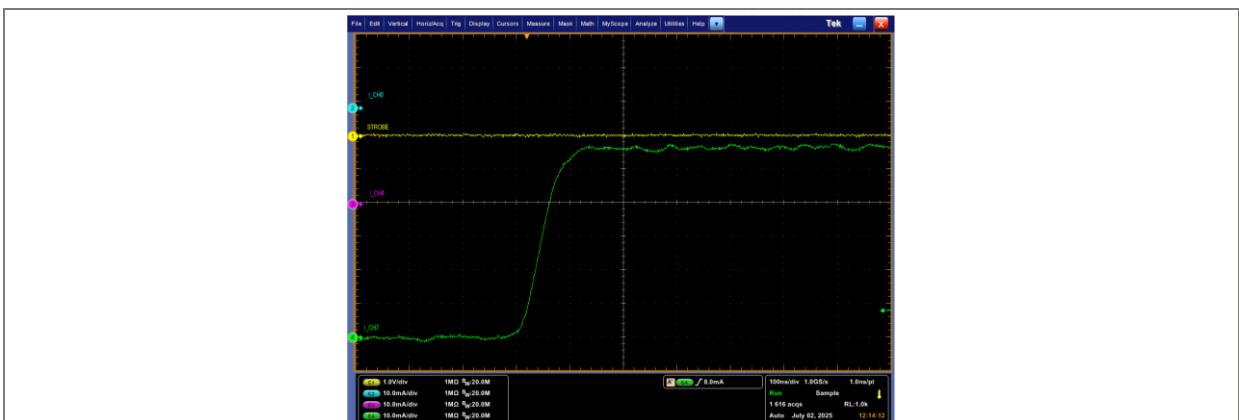

Figure 12: Current sink rise time

- (1)  $I_{CH7} = 60\text{mA}$

- (2) Slew rate = 0

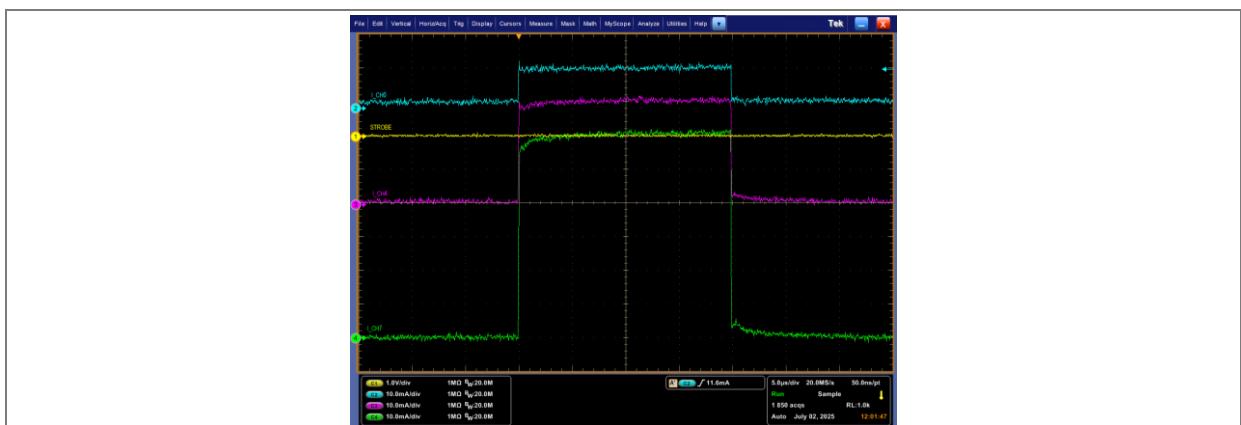

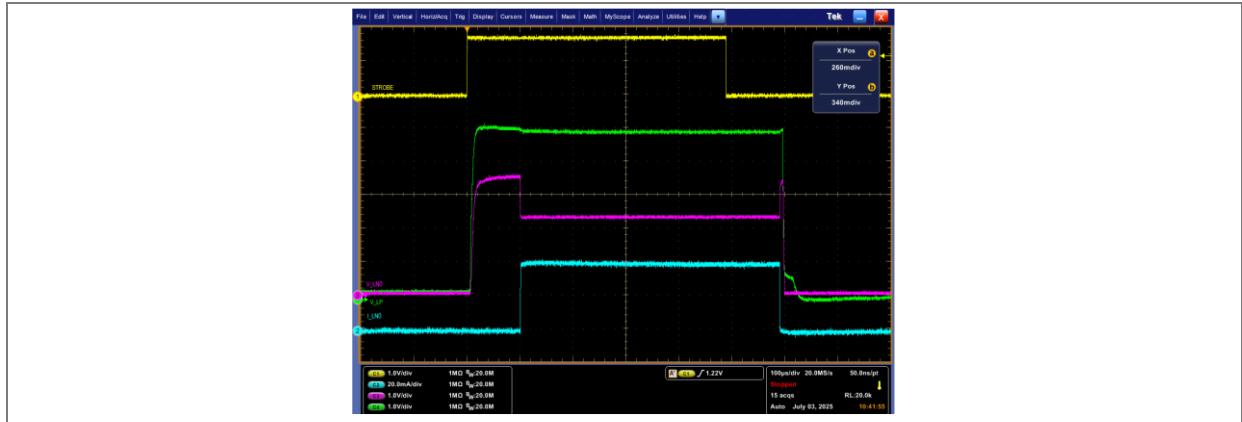

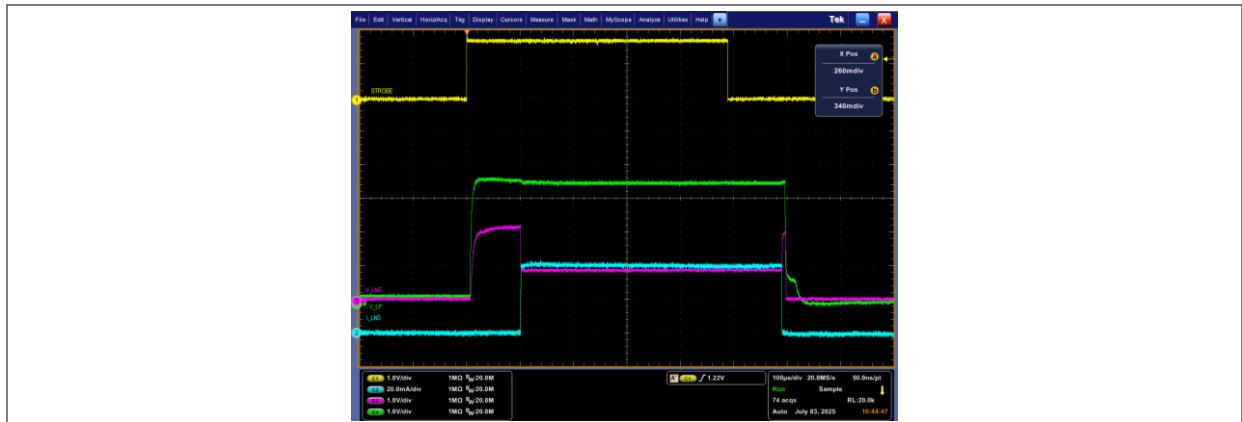

**Figure 13: Typical channel enable**

- (1) V\_LP (VLED, green) = 5V; V\_LN0 (purple)

- (2) I\_CH0 (blue) = 40mA

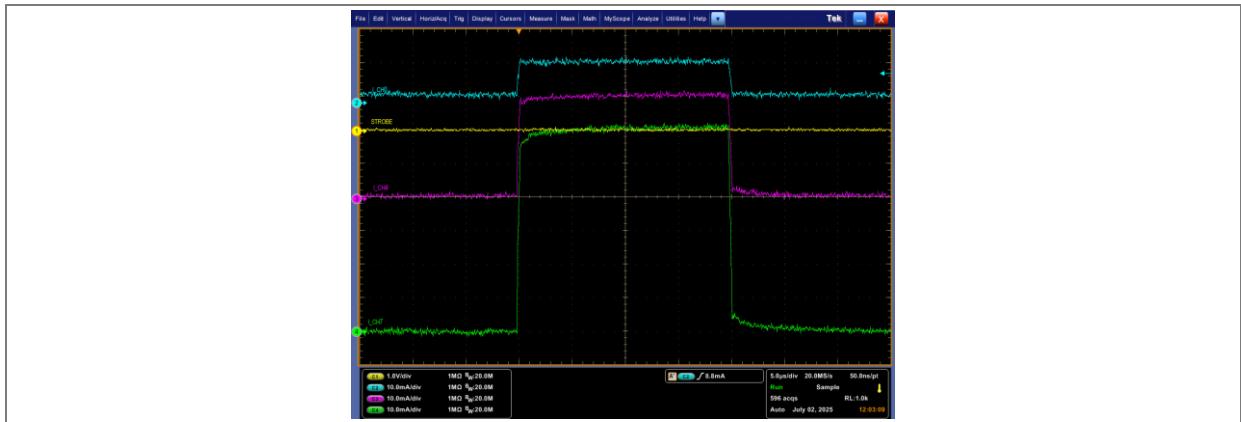

**Figure 14: Typical channel enable**

- (1)  $V_{LP}$  (VLED, green) = 3.6V;  $V_{LN0}$  (purple)

- (2)  $I_{CH0}$  (blue) = 40mA

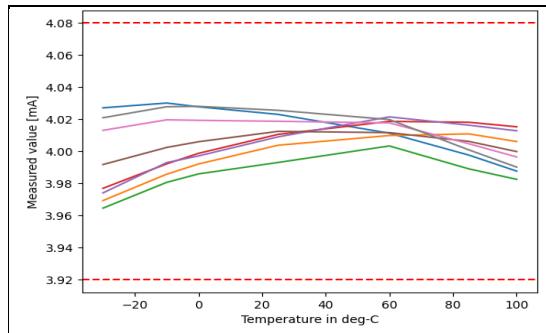

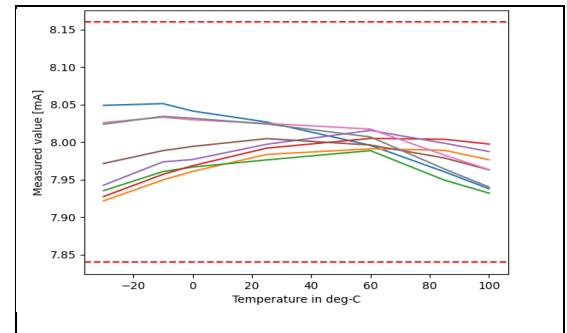

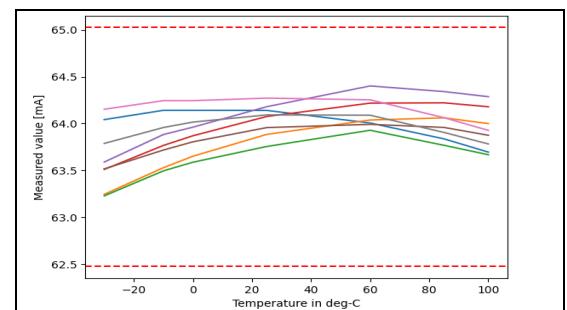

Figure 15: Typical channel matching @ 4mA<sup>(1)</sup>Figure 16: Typical channel matching @ 8mA<sup>(1)</sup>

(1) Typical Channel (LNx) matching of 1 device over temperature. Individual colored lines represent L<sub>Nx</sub> current/LED current.

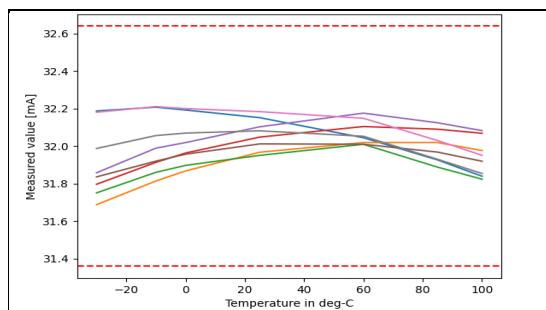

Figure 17: Typical channel matching @ 32mA<sup>(1)</sup>Figure 18: Typical channel matching @ 64mA<sup>(1)</sup>

(1) Typical Channel (LNx) matching of 1 device over temperature. Individual colored lines represent L<sub>Nx</sub> current/LED current.

## 7 Functional description

### 7.1 Operation modes

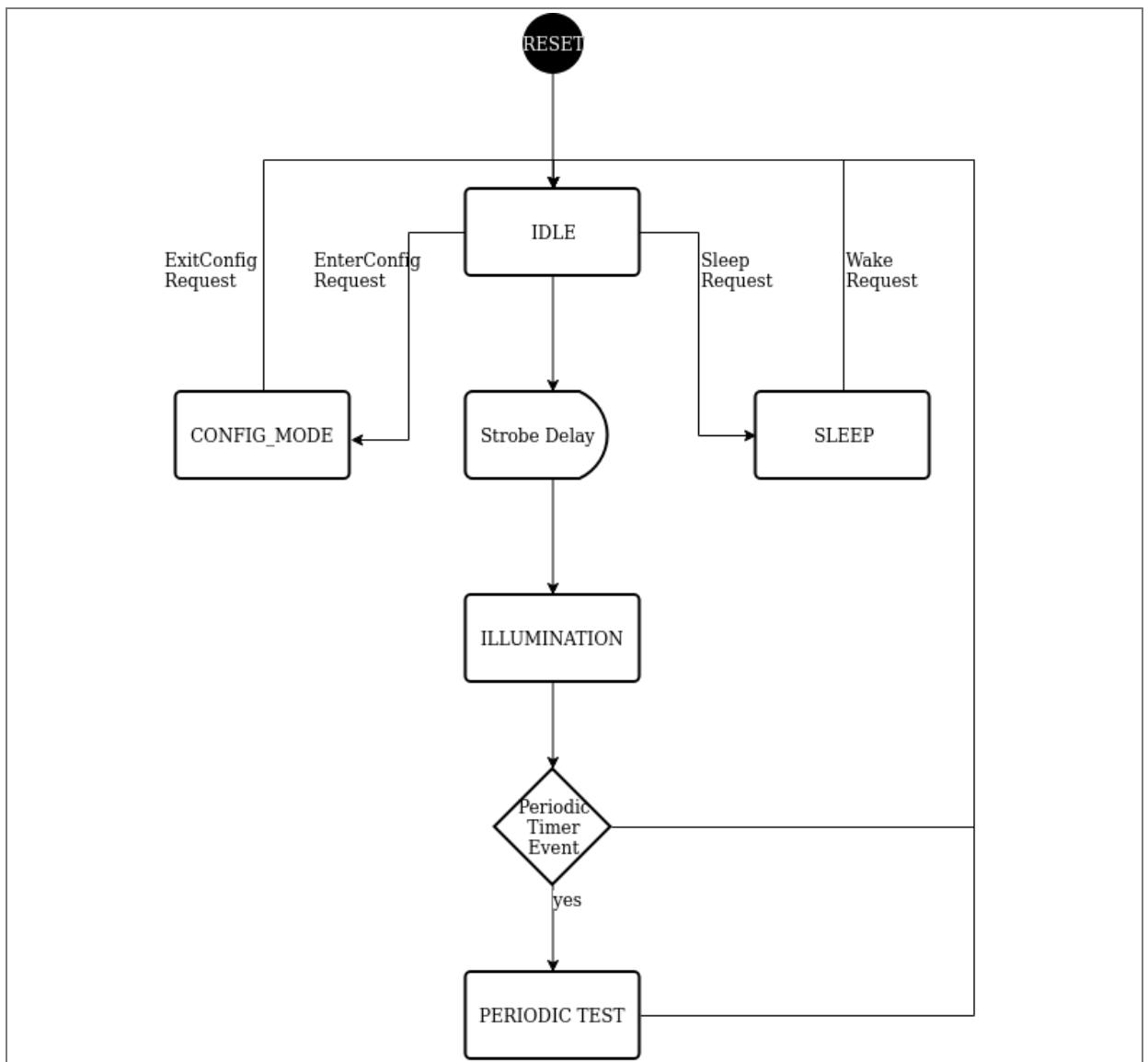

Figure 19: Operation modes flow diagram

### 7.1.1 Sleep mode

The Sleep mode can be entered by writing the SLEEP command to the I2C\_COMMAND\_CODE register (in I<sup>2</sup>C mode) or by executing the CCC SLEEP (in I3C mode).

The Sleep mode can only be left by writing the WAKE command to the I2C\_COMMAND\_CODE register (in I<sup>2</sup>C mode) or by executing the CCC WAKE (in I3C mode).

During Sleep mode the following register access is possible:

- Writing to I2C\_COMMAND\_CODE register

- Reading SYSTEM\_STATE register

- All other writes to any address don't take any effect

- All other reads to any address return 0xFFFF

When the device uses I3C the following direct and indirect CCC operations are possible, with the following exceptions:

- ENEC/DISEC will only take effect after WAKE has been sent

- CCC Strobe, ClearIRQ, and RunSelfTest don't trigger any CPU task

- IBI generation and IRQ\_N assertion is delayed by the oscillator start time

### 7.1.2 Config mode

Safety relevant registers can only be changed from I3C when the "config\_mode" bit is set. Within this mode, no new illumination cycle is allowed to happen.

Entering this mode is protected by a 32-bit key which is stored in CONFIG\_KEY\_COMP register. Before sending the change mode CCC, the register CONFIG\_KEY needs to contain the same key as CONFIG\_KEY\_COMP in order to toggle the config\_mode bit. The CONFIG\_KEY registers get cleared to 0 on each try to toggle the config\_mode bit.

This means that before entering and before exiting the config mode, the specific key needs to be stored in the CONFIG\_KEY registers.

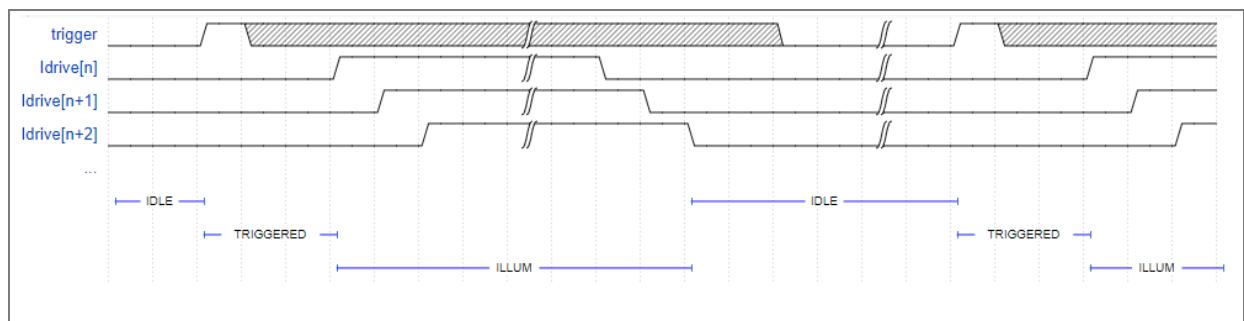

### 7.1.3 Illumination sequence & STROBE mode

The illumination sequence always starts in IDLE state when a strobe is asserted.

The strobe will enter state “TRIGGERED” depending on the strobe delay defined in CH\_DLY register (Address 0x1A24) bit “TD\_TRIGDLY” or skip this state when TD\_TRIGDLY is “0”.

The state ILLUM lasts from the first channel that is turned on to the last channel that is turned off. In STROBE mode the illumination duration is defined internally by the TD\_ILLUM register (Address 0x1A00).

Figure 20: Illumination sequence

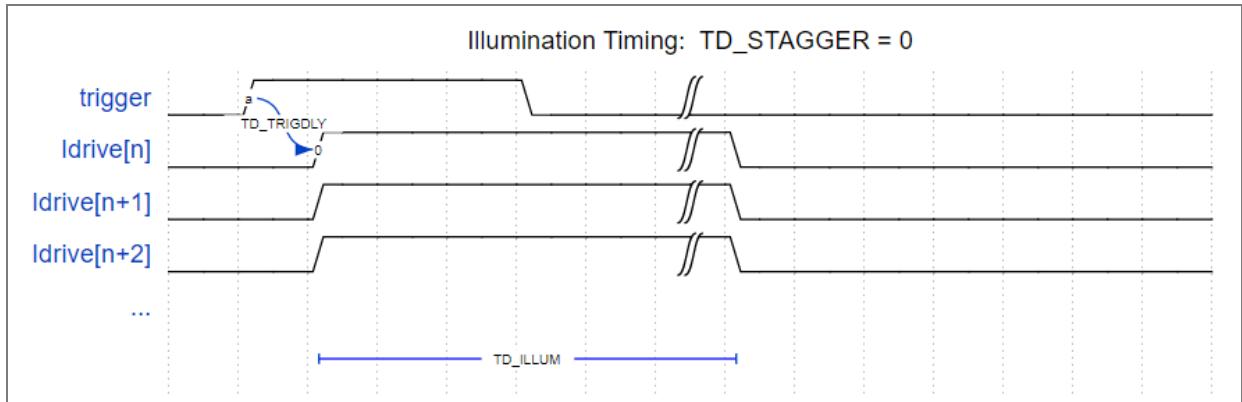

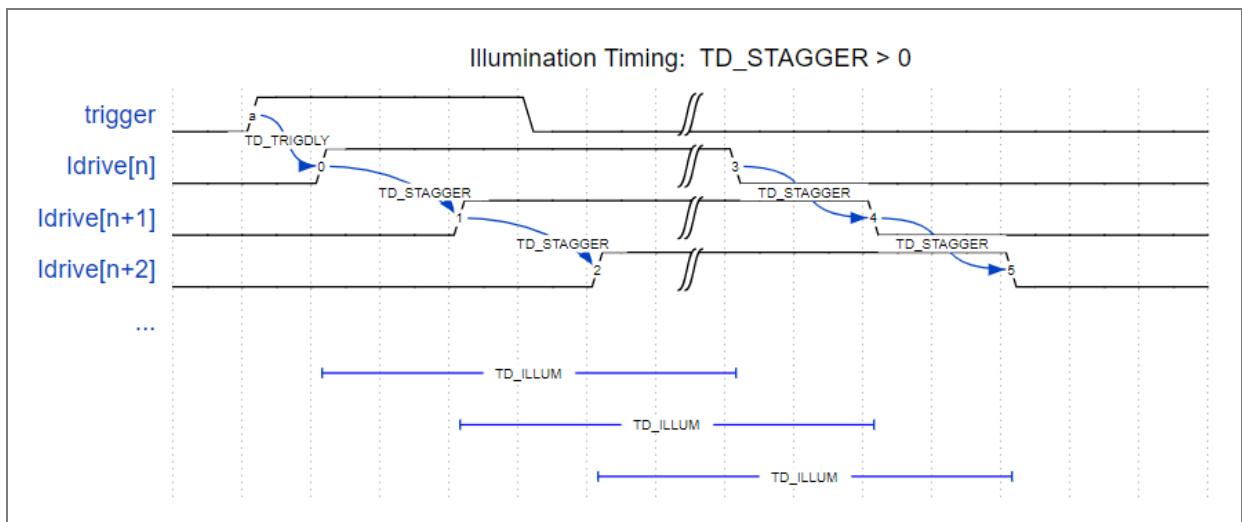

#### 7.1.3.1 Stagger delay

Stagger delay is controlled by CH\_DLY register (Address 0x1A24) bit “TD\_STAGGER” and allows to add a delay before the next channel group is turned on/off.

#### Information:

A group can contain 1 or more channels.

Figure 21: TD\_STAGGER = 0

(1) TD\_STAGGER = 0: All channels are turned on at the same time.

Figure 22: TD\_STAGGER > 0

The channels turn on one by one, each delayed by TD\_STAGGER. The channel with the lowest number will turn on first.

### 7.1.4 Channel grouping

Grouping is defined by the CH\_GROUP register (Address 0x1A22) and CH\_ENABLE register (Address 0x1A26). Channels that are turned off will be skipped and will not add a stagger delay.

The examples below illustrate some channel grouping schemes.

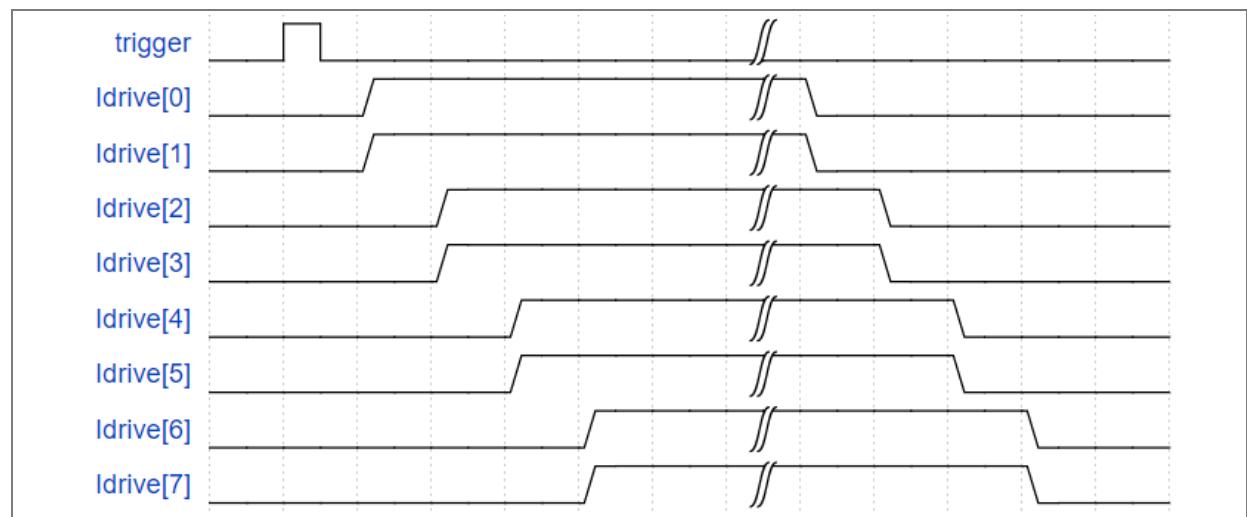

#### 7.1.4.1 Example: CHAN\_GROUP is 0x155 & CHAN\_ENABLE is 0x3FF

Figure 23: Channel group example 1

(1) Channel groups are 0+1, 2+3, 4+5, 6+7

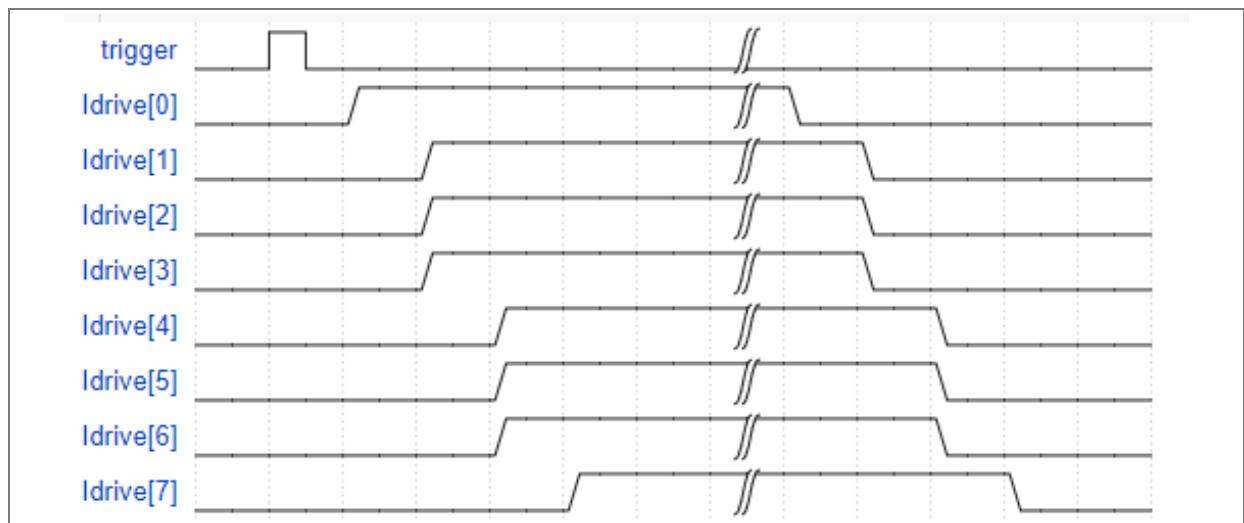

#### 7.1.4.2 Example: CHAN\_GROUP is 0x93 & CHAN\_ENABLE is 0x3FF

Figure 24: Channel group example 2

(1) Channel groups are 0, 1+2+3, 4+5+6, 7

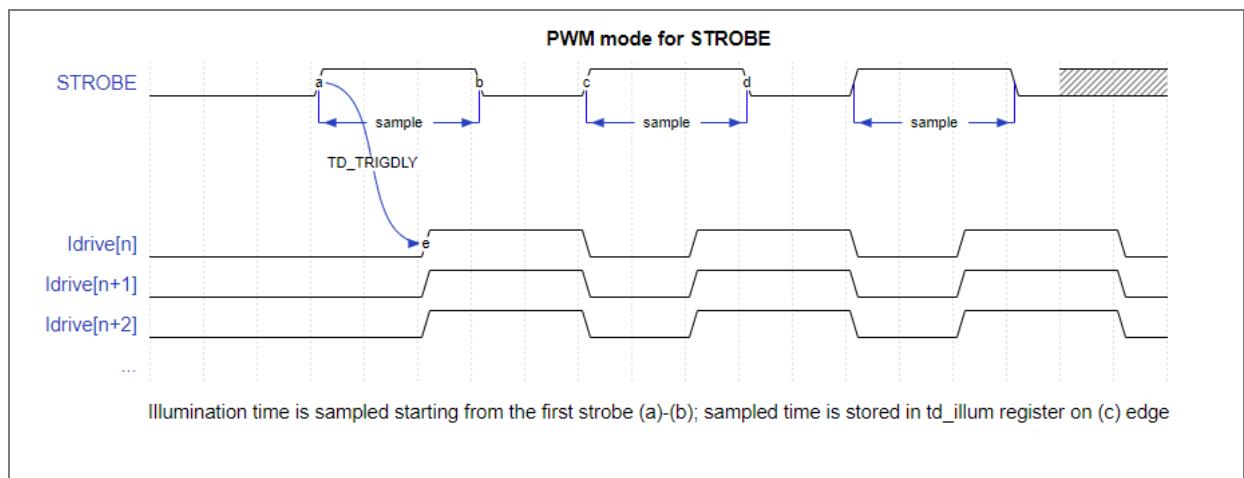

### 7.1.5 Direct PWM mode (1 PWM input)

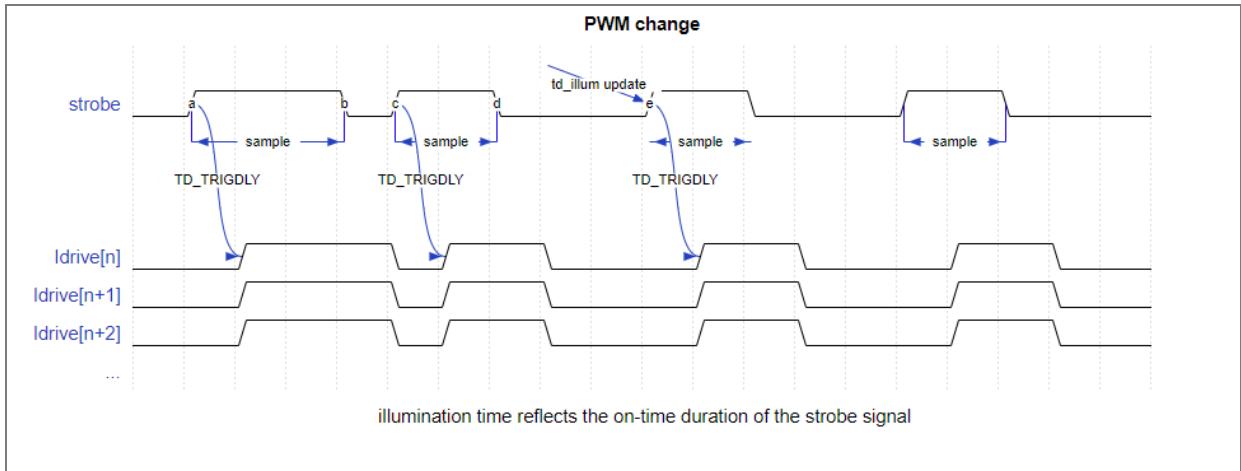

In direct PWM mode the illumination duration can be controlled by “STROBE1\_PWM1” input used as a direct PWM source. If enabled by the PWM\_CTR register (Address 0x1A32) bit “*pwm\_illum\_enable*” the “STROBE1\_PWM1” signal on-time determines the illumination duration. Additionally, “TD\_ILLUM register (Address 0x1A00) shows sampled illumination duration. Illumination is still triggered by the rising edge of “STROBE1\_PWM1” signal, with latency defined in CH\_DLY register (Address 0x1A24) bit “TD\_TRIGDLY”.

Figure 25: External PWM mode 1

Sampling is continuous and the illumination duration follows the on-time of the “STROBE1\_PWM1” signal with *TD\_TRIGDLY* latency.

TD\_ILLUM register (Address 0x1A00) is updated with newly sampled duration with latency of the one PWM cycle.

Figure 26: Illumination time register update

Table 5: External PWM mode constraints

| Symbol            | Parameter         | Min                       | Typ | Max   | Unit | Note                                                                                                                        |

|-------------------|-------------------|---------------------------|-----|-------|------|-----------------------------------------------------------------------------------------------------------------------------|

| T <sub>HIGH</sub> | Strobe high time  | 20                        |     | 15000 | μs   |                                                                                                                             |

| T <sub>LOW</sub>  | Strobe low time   | 65+T <sub>stagger</sub> * |     |       | μs   | *T <sub>stagger</sub> - time needed to perform all the staggering for all groups, if staggering is disabled equals to zero. |

| P                 | PWM period        | 0.2                       |     | 16.6  | ms   | PWM1 and PWM2 shall have the same period in dual PWM input mode.                                                            |

| F                 | PWM frequency     | 60                        |     | 5000  | Hz   |                                                                                                                             |

| DC                | Duty cycle        | 10                        |     | 90    | %    |                                                                                                                             |

| T <sub>skew</sub> | PWM1&2 input skew |                           |     | 10    | μs   | Maximum skew between PWM1 and PWM2 input in all modes.                                                                      |

Figure 27: External PWM constraints

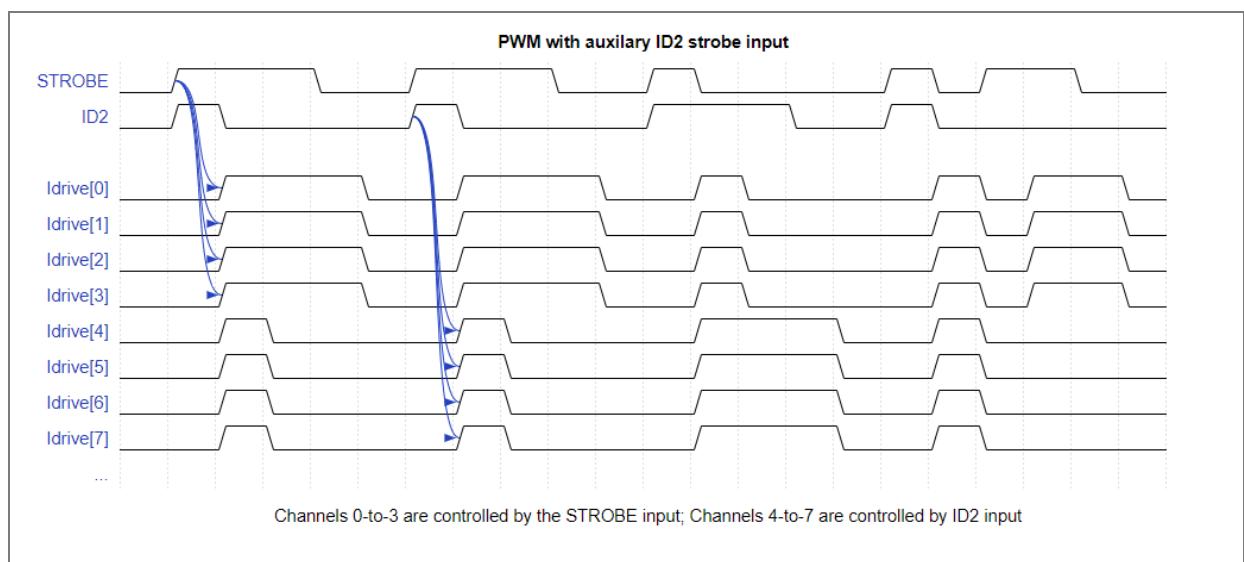

### 7.1.6 Direct PWM mode (2 PWM inputs)

Illumination duration for channels in PWM Mode can also be controlled by the ID2\_PWM2 input, which can be used as 2<sup>nd</sup> PWM input signal.

The mode is enabled by setting pwm\_grp\_split field in the PWM\_CTR register (Address 0x1A32) to the non-zero value.

The value in the field pwm\_grp\_split is used to split the channels into two groups. The illumination duration for the channels in the first group is controlled then by the STROBE1\_PWM1 input. The illumination duration for the channels in the second group is controlled by the ID2\_PWM2 input.

Figure 28: External PWM mode with 2 inputs (dual trigger)

#### 7.1.6.1 Trigger adjustment for the PWM mode with 2 strobe inputs

In default case the illumination sequence is triggered by the first rising edge of either input. The triggering moment can be adjusted by setting the `pwm_trig` field in the `PWM_CTR` register (Address 0x1A32) to non-zero value.

- 0x0 – Default, `STROBE_PWM1` or `ID2_PWM2`: Illumination is triggered by the first rising edge of either signal.

- 0x1 – `STROBE_PWM1` and `ID2_PWM`: Illumination is triggered in the moment both signals become high.

- 0x2 – `STROBE_PWM1` only: Illumination for both groups is triggered by the rising edge of `STROBE_PWM1` input.

- 0x3 – `AUX` only: Illumination for both groups is triggered by the `ID2_PWM2` signal rising edge.

The skew between the rising edges of both inputs in all cases shall be less than 10µs.

If the other signal edge doesn't come within the skew window, the illumination sequence for this channels group won't start on this cycle.

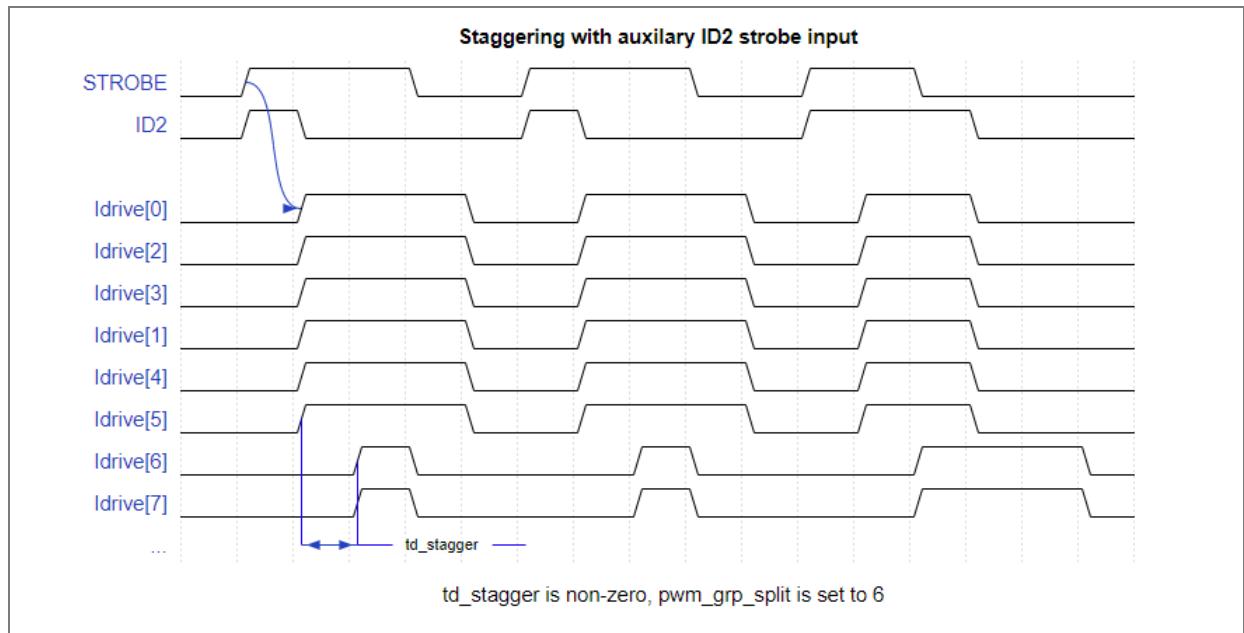

### 7.1.6.2 Staggering for the PWM mode with 2 PWM inputs

If “*td\_stagger*” field in register CH\_DLY register (Address 0x1A24) is set to non-zero value, it applies as a delay in the illumination between channels group assigned to the STROBE\_PWM1 input and a group assigned to the ID2\_PWM2 input.

Note that in this mode the grouping defined in the CH\_GROUP register (Address 0x1A22) is ignored, the grouping follows “*pwm\_grp\_split*” field setting in register PWM\_CTR register (Address 0x1A32).

Figure 29: Stagger delay with 2 external PWM inputs

## 7.2 Safety monitors

AS1181 integrates several safety features to detect open or shorted LEDs and to avoid unwanted overcurrent situations also under single fault conditions.

Safety features are implemented on the high side (LP - Anode) and low side (LNx - Cathode) of the LEDs as shown in the detailed block diagram below. All safety features are operating fully self-contained and do not require an external host to shut down illumination.

Figure 30: Block diagram safety monitors

## 7.2.1 High side safety monitors

### 7.2.1.1 Power switch / overcurrent detection

The current applied to the LEDs is measured and compared to an internal reference current in the high side current path (LP node). This reference current defines the turn off threshold and can be programmed in HSCS\_SEL register (Address 0x1A30). The individual channel current limits can be defined in CURR\_LIM0 register (Address 0x1A12) to CURR\_LIM7 register (Address 0x1A20).

### 7.2.1.2 LP node open/short detection

LP shorts and open (anode connection of the LED) are detected using current sources in the “short LP” section of Figure 26 while the power switch is off to prevent accidental illumination or uncontrolled current paths outside the LEDs.

## 7.2.2 Low side safety monitors

### 7.2.2.1 Open and short LED detection

Checks for open and shorted LEDs are done at the cathode connection (LN<sub>x</sub>) of the LEDs. If the voltage on the LN<sub>x</sub> pin is higher than a programmed threshold voltage a shorted LED is detected and if the voltage on the LN<sub>x</sub> pin is lower than a programmed threshold open LEDs are detected. The detection thresholds are pre-programmed in OTP and can be adjusted in the COMP\_LVL\_SHORT register (Address 0x1A4C) and COMP\_LVL\_OPEN register (Address 0x1A4E).

## 7.2.3 Digital safety monitors

### 7.2.3.1 Illumination time monitor

The illumination time monitor is continuously sampling the PWM ON time applied via both inputs and comparing the result with the value programmed in “TD\_ILLUM\_MAX register (Address 0x1A36)”. In PWM mode the ON time (HIGH Time) is constrained to be maximum 15ms. Therefore, the value in the TD\_ILLUM\_MAX register shall be less the 15ms in this mode. (Refer to Table 5: External PWM mode constraints).

If the actual PWM ON time is longer than the value programmed the current sinks get turned off and the respective interrupt flag is set.

Figure 27 shows the actual implementation – in the 3<sup>rd</sup> frame (STROBE = yellow) the PWM ON time changes from 4ms to 10ms – TD\_ILLUM\_MAX is programed to 4.1ms.

The current sink (blue) is turned off immediately and the interrupt IRQ\_N (green) is pulled to GND. The interrupt “Illumination Duration” has been set and is informing the Host.

Figure 31: Illumination time monitor example

#### 7.2.3.2 Strobe rate monitor in STROBE mode

The strobe rate monitor measures the applied strobe signal frequency and compares it to the value stored in TD\_TRATE\_MAX register (Address 0x1A34). If the applied strobe signal is too fast, an interrupt is set to inform the host. Note that the strobe rate monitor is not available in direct PWM mode with 1 or 2 inputs.

#### 7.2.4 BIST (Built-in-self test)

A built-in-self test is implemented periodically check the device safety monitors.

After power-on-reset the digital BIST is checking RAM, ROM and OTP followed by the analog BIST checking the following circuits:

1. VLED voltage monitor and error injection to test comparator toggling.

2. VP18 voltage monitor and error injection to test comparator toggling.

3. Temperature monitor and error injection to test comparator toggling.

4. LN shorts and open tests.

5. LN comparator and error injection to test comparator toggling.

6. LP shorts and open tests.

7. LP comparator error and error injection to test comparator toggling.

8. High-side power switch / Overcurrent detection" circuit operation.

**Note:** Error injection tests are done after power on-reset only while LN<sub>x</sub> & LP short/open tests are done continuously.

#### 7.2.5 Temperature shutdown

The device integrates an on-chip temperature supervision for over and under temperature situations. If the device is exposed to too high or too low temperatures it will shut down the current sinks, sets respective interrupt and informs the host.

## 7.3 Interrupt controller

Interrupt requests are sent to output pin IRQ\_N. This signal is active low and the pin is configured as open drain output.

The condition to trigger an interrupt for a specific source is:

- If an interrupt source is ASSERTED, ENABLED and NOT MASKED, then the IRQ\_N is asserted.

- If an interrupt source is asserted, then it is captured in the interrupt status register IRQ\_STATUS0 register (Address 0x1AA4), IRQ\_STATUS1 register (Address 0x1AA6) and IRQ\_STATUS2 register (Address 0x1AA8).

- An interrupt is enabled if the corresponding enable register bit is set to 1 in the following registers: IRQ\_ENABLE0 register (Address 0x1A38), IRQ\_ENABLE1 register (Address 0x1A3A) and IRQ\_ENABLE2 register (Address 0x1A3C).

- An interrupt can be masked(inhibited) if the corresponding mask register bit is set to 1 in the following registers: IRQ\_MASK0 register (Address 0x1AB0), IRQ\_MASK1 register (Address 0x1AB2), IRQ\_MASK2 register (Address 0x1AB4).

- IRQ\_N is latched on the first interrupt occurrence.

- IRQ\_N is not cleared until all interrupt status registers containing a set interrupt are read (reading the interrupt status registers clears them).

- The IRQ\_N output signal is the NOR-function of all interrupt sources.

### 7.3.1 Interrupt sources

AS1181 has the following interrupt sources:

Interrupts 0-15 can be managed with the following registers:

- IRQ\_ENABLE0 register (Address 0x1A38)

- IRQ\_STATUS0 register (Address 0x1AA4)

- IRQ\_HISTORY0 register (Address 0x1AAA)

- IRQ\_MASK0 register (Address 0x1AB0)

Table 6: Interrupt sources 0-15

| Bit | Source               | Severity | Interrupt type | Description                                                                             |

|-----|----------------------|----------|----------------|-----------------------------------------------------------------------------------------|

| 0   | fault                | Highest  | Pulse/level    | System fault (asserted by safety monitor)<br>(The OR-function of all 'critical' errors) |

| 1   | fv_tc_done           | Info     | Pulse          | Temperature compensation completed                                                      |

| 2   | vload_adj_request    | Info     | Pulse          | Vload adjust request – set when idrive_undervoltage is asserted                         |

| 3   | asic_test_done       | Info     | Pulse          | RunSelfTest completed                                                                   |

| 4   | boot_complete        | Info     | Pulse          | Startup(Boot) completed                                                                 |

| 5   | task_done            | Info     | Pulse          | Task done                                                                               |

| 6   | periodic_test_done   | Info     | Pulse          | Periodic test done ("max_timer")                                                        |

| 7   | illum_start          | Info     | Pulse          | Illumination start of first channel                                                     |

| 8   | illum_end            | Info     | Pulse          | Illumination end of last channel                                                        |

| 9   | over_temp            | Critical | Level          | Over temperature (temp. > 125deg)                                                       |

| 10  | idrive_overvoltage   | Info     | Pulse          | Overvoltage on any active channel                                                       |

| 11  | idrive_undervoltage  | Info     | Pulse          | Undervoltage on any active channel                                                      |

| 12  | trigger_rate_error   | Critical | Pulse          | Trigger rate check ("min_timer")                                                        |

| 13  | ecc_error            | Critical | Level          | OTP ECC error                                                                           |

| 14  | idrive_ramp_error    | Critical | Pulse          | Channel Ramp-down error                                                                 |

| 15  | illum_duration_error | Critical | Pulse          | Illumination time error                                                                 |

Interrupts 16-31 can be managed with the following registers:

- IRQ\_ENABLE1 register (Address 0x1A3A)

- IRQ\_STATUS1 register (Address 0x1AA6)

- IRQ\_HISTORY1 register (Address 0x1AAC)

- IRQ\_MASK1 register (Address 0x1AB2)

Table 7: Interrupt sources 16-31

| Bit | Source                | Severity | Interrupt type | Description                                           |

|-----|-----------------------|----------|----------------|-------------------------------------------------------|

| 0   | osc_error             | Critical | Pulse          | Oscillator period error                               |

| 1   | watchdog_timeout      | Critical | Pulse          | Watchdog timeout error                                |

| 2   | rload_test_error      | Critical | Pulse          | Rload test failure                                    |

| 3   | hs_overcurrent        | Critical | Pulse/level    | HS switch overcurrent error (BIST & continuous check) |

| 4   | curr_lim_hi_overrun   | Critical | Level          | Overcurrent error on any channel                      |

| 5   | curr_lim_lo_underrun  | Critical | Level          | Undercurrent error on any channel                     |

| 6   | supply_overvoltage    | Critical | Level          | Overvoltage error on VP18 or Vload                    |

| 7   | supply_undervoltage   | Critical | Level          | Undervoltage error on VP18 or Vload                   |

| 8   | lp_short_open_error   | Critical | Pulse/level    | LP short or open failure (BIST & continuous check)    |

| 9   | ln_short_open_error   | Critical | Pulse/level    | LN short or open failure (BIST & continuous check)    |

| 10  | idrive_feedback_error | Critical | Level          | idrive vs. analog current comparison failure          |

| 11  | otp_test              | Critical | Pulse          | OTP read check error                                  |

| 12  | ram_bist              | Critical | Pulse          | RAM BIST error                                        |

| 13  | rom_bist              | Critical | Pulse          | ROM BIST error                                        |

| 14  | Not used              |          |                |                                                       |

| 15  | Not used              |          |                |                                                       |

Interrupts 32-38 can be managed with the following registers:

- IRQ\_ENABLE2 register (Address 0x1A3C)

- IRQ\_STATUS2 register (Address 0x1AA8)

- IRQ\_HISTORY2 register (Address 0x1AAE)

- IRQ\_MASK2 register (Address 0x1AB4)

Table 8: Interrupt sources 32-38

| Bit | Source              | Severity | Interrupt type | Description           |

|-----|---------------------|----------|----------------|-----------------------|

| 0   | vload_monitor_error | Critical | Pulse          | VLOAD BIST fail       |

| 1   | vp18_monitor_error  | Critical | Pulse          | VP18 BIST fail        |

| 2   | temp_detect_error   | Critical | Pulse          | Temperature BIST fail |

| 3   | adc_bist_error      | Critical | Pulse          | ADC BIST fail         |

| 4   | Is_overcurrent      | Critical | Level          | vgate_low             |

| 5   | driver_gate_short   | Critical | Level          | driver_gate_max on    |

| 6   | ldo_overcurrent     | Critical | Level          | LDO overcurrent       |

### 7.3.2 Interrupt status & history

Reading the 3 “IRQ\_STATUS” registers will automatically clear the corresponding interrupt status bits.

Before clearing is done, the contents of “IRQ\_STATUS” are copied into register IRQ\_HISTORY0 register (Address 0x1AAA), IRQ\_HISTORY1 register (Address 0x1AAC) and IRQ\_HISTORY2 register (Address 0x1AAE) to backup the interrupt status.

The interrupt output signal IRQ\_N will be de-asserted only after the 3 status registers have been read.

The I3C CCC command 'ClearFaults' clears all status bits in IRQ\_STATUS0 to IRQ\_STATUS3 with one exception IRQ\_STATUS[0] (bit 0, "fault") will only be cleared with I3C CCC command 'Reset'.

**Note:** Only interrupt status bits of type 'pulse' (see Table 6, Table 7, Table 8) will be cleared immediately. Interrupt status bits of interrupts with type 'level' will be cleared after interrupt source has vanished.

## 7.4 Serial interface description (I<sup>2</sup>C and I3C)

The device supports both I<sup>2</sup>C and I3C interface. The I3C Target is implemented according to the MIPI-I3C Basic specification v1.1.1. The Target module is connected as a master on the internal system bus.

The default communication mode for AS1181 is I<sup>2</sup>C, where no in-band interrupts are generated. In the I<sup>2</sup>C mode 50ns spike filters in the pad cells are enabled.

The I<sup>2</sup>C spike filter in the pads get disabled after I3C communication is detected in the address header (header needs to be transported with I<sup>2</sup>C timings).

In-Band-Interrupts are initially disabled and need to be enabled with the ENEC CCC.

I<sup>2</sup>C is supported up to 1Mbps (fast mode plus).

### 7.4.1 Operation in legacy I<sup>2</sup>C mode

I3C CCC messages are not supported in I<sup>2</sup>C systems, there are the following limitations:

- Broadcast Strobe can be initiated by the external signal or by writing the Strobe command code to the I2C\_COMMAND\_CODE register.

- Interrupts are only asserted on output pin IRQ\_N

### 7.4.2 I3C supported features

Table 9: I3C feature support

| Feature                                              | Supported |

|------------------------------------------------------|-----------|

| Single Data Rate (SDR) messaging mode up to 12.5 MHz | Yes       |

| High Data Rate (HDR) messaging modes                 | No        |

| Dynamic Address Assignment (DAA)                     | Yes       |

| Request In-Band Interrupts                           | Yes       |

| Generate Hot-Join events                             | No        |

| Controller device capability                         | No        |

| Legacy I <sup>2</sup> C messaging                    | Yes       |

| Timing control                                       | No        |

### 7.4.3 I3C CCC commands

I3C devices according to MIPI specification support various common command codes (CCC) to control certain features of the device.

Following Broadcast and Direct Vendor Common Command Codes (VCCCs) are defined specifically for AS1181. There is no payload byte on any of the VCCCs.

Table 10: I3C CCC commands

| Name              | Broadcast code | Direct code | Description                                                                                                                                                                     |

|-------------------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset             | 0x61           | 0xE1        | Resets the device.                                                                                                                                                              |

| Strobe            | 0x62           | 0xE2        | Initiates an illumination sequence and is the equivalent of asserting the hardware strobe input signal.                                                                         |

| ClearIRQ          | 0x63           | 0xE3        | Clears all IRQ_STATUS registers. This can be used after an IBI-Request has been acknowledged.                                                                                   |

| Sleep             | 0x64           | 0xE4        | Sends the device from IDLE into SLEEP state. I3C target remains powered enabling the subsequent commands to be processed, use the Wake CCC to wake the device from SLEEP state. |

| Wake              | 0x65           | 0xE5        | Wake the device from internal SLEEP state to IDLE state.                                                                                                                        |

| ChangeMode        | 0x66           | 0xE6        | Compares the content of CONFIG_KEY registers with CONFIG_KEY_COMP and toggles the config_mode bit on a match. CONFIG_KEY will always be cleared after the compare is done.      |

| <i>Do not use</i> | 0x67           | 0xE7        |                                                                                                                                                                                 |

| AnalogSelfTest    | 0x68           | 0xE8        | Executes all analog BISTs which are also executed during startup.                                                                                                               |

| PeriodicTest      | 0x69           | 0xE9        | Executes the periodic test sequences.                                                                                                                                           |

| <i>Do not use</i> | 0x6A           | 0xEA        |                                                                                                                                                                                 |

| DigitalSelfTest   | 0x6B           | 0xEB        | Executes all digital BISTs which are also executed during startup.                                                                                                              |

| <i>Do not use</i> | 0x6C - 0x6F    | 0xEC - 0xEF |                                                                                                                                                                                 |

| <i>Do not use</i> | 0x70           | 0xF0        |                                                                                                                                                                                 |

| <i>Do not use</i> | 0x71           | 0xF1        |                                                                                                                                                                                 |

| VfMeasurement     | 0x72           | 0xF2        | Runs a VF Measurement on a selected channel. Can only be executed in CONFIG_MODE.                                                                                               |

| <i>Do not use</i> | 0x73 - 0x77    | 0xF3 - 0xF7 |                                                                                                                                                                                 |

| <i>Do not use</i> | 0x78 - 0x7E    | 0xF8 - 0xFE |                                                                                                                                                                                 |

| <i>Do not use</i> | 0x7F           | -           |                                                                                                                                                                                 |

**Note:** After a direct CCC has been sent to the device a STOP condition needs to follow before the next CCC can be sent.

#### 7.4.4 Dynamically assigned addresses

The device supports I3C Dynamic Address Assignment, which is initiated by the external host controller with the broadcast common command code 'Enter Dynamic Address Assignment' (ENTDAA).

The device supports Dynamic Address Assignment in the condition where the external host can overwrite the device statically assigned address using the common command code 'Set Dynamic Address from Static Address' (SETDASA).

After an address is dynamically assigned, the device only responds to the newly assigned address and no longer responds to the default target address. The dynamically assigned address shall be used until the device is reset, at which point the device shall return to its default target address.

#### 7.4.5 Default I<sup>2</sup>C and I3C slave address

The default 7-bit I<sup>2</sup>C / I3C address is defined as follows. The ID1 and ID0 are input pins of the device.

Table 11: Serial interface slave address configuration

| A6 | A5 | A4 | A3 | A2 | A1  | A0  |

|----|----|----|----|----|-----|-----|

| 1  | 0  | 1  | 0  | 0  | ID1 | ID0 |

Note that the I<sup>2</sup>C / I3C static address space is from **50h** to **53h** depending on the input levels of ID1 and ID0.

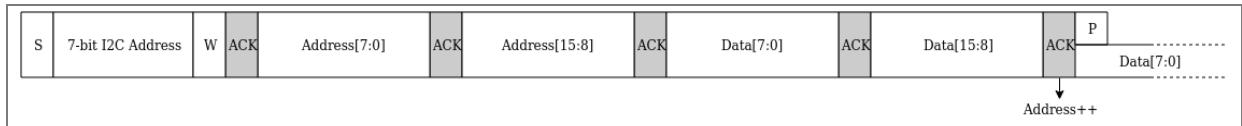

### 7.4.6 I<sup>2</sup>C read & write command

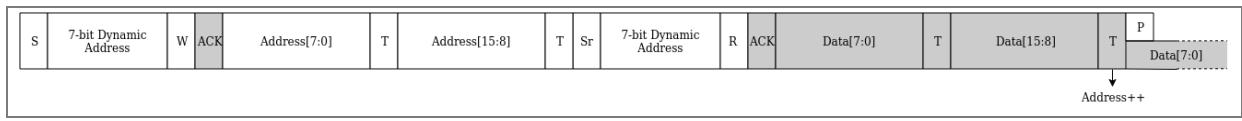

Figure 32: I<sup>2</sup>C write data

Figure 33: I<sup>2</sup>C read data

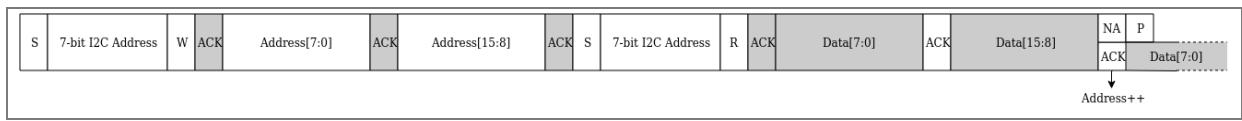

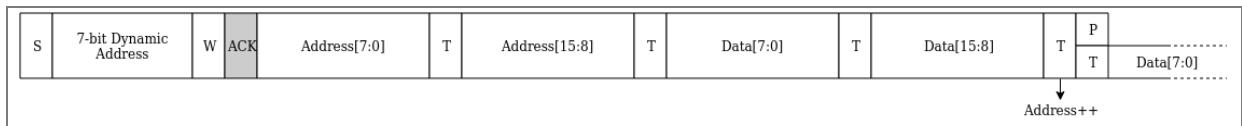

### 7.4.7 I3C read & write command

Figure 34: I3C private write data

Figure 35: I3C private read data

## 8 Register description

### 8.1 Detailed register description

#### 8.1.1 TD\_ILLUM register (Address 0x1A00)

Table 12: TD\_ILLUM register (Write Access when system state == idle)

| Addr: 0x1A00 |                 | TD_ILLUM |        |                                                                                                                                                                                                                                                                                                           |

|--------------|-----------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field       | Default  | Access | Bit description                                                                                                                                                                                                                                                                                           |

| 10:0         | <i>td_illum</i> | 0x0      | RW     | <p>LED illumination duration defined in [μs].</p> <p><b>Note:</b></p> <p>If <code>pwm_illum_enable</code> is high this field shows sampled illumination time based on STROBE pin as a PWM source.</p> <p>In pwm mode h'7fff sampled value means constant high STROBE input and constant illumination.</p> |

### 8.1.2 CURR0 register (Address 0x1A02)

Table 13: CURR0 register (Write Access when system state == idle)

| Addr: 0x1A02 |                     | CURR0   |        |                                                                                                                                                                                                                                                                                |

|--------------|---------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field           | Default | Access | Bit description                                                                                                                                                                                                                                                                |

| 7:0          | <i>curr0</i>        | 0x0     | RW     | <p>LED current for channel 0. Used for internal sensing.</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr0</i> and <i>curr0_target</i> shall be programmed to the same value.</p> |

| 15:8         | <i>curr0_target</i> | 0x0     | RW     | <p>Target LED current for channel 0</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr0</i> and <i>curr0_target</i> shall be programmed to the same value.</p>                      |

### 8.1.3 CURR1 register (Address 0x1A04)

Table 14: CURR1 register (Write Access when system state == idle)

| Addr: 0x1A04 |                     | CURR1   |        |                                                                                                                                                                                                                                                                  |

|--------------|---------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field           | Default | Access | Bit description                                                                                                                                                                                                                                                  |

| 7:0          | <i>curr1</i>        | 0x0     | RW     | <p>LED current for channel 1. Used for internal sensing.</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields currx and currx_target shall be programmed to the same value.</p> |

| 15:8         | <i>curr1_target</i> | 0x0     | RW     | <p>Target LED current for channel 1</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields currx and currx_target shall be programmed to the same value.</p>                      |

### 8.1.4 CURR2 register (Address 0x1A06)

Table 15: CURR2 register (Write Access when system state == idle)

| Addr: 0x1A06 |                     | CURR2   |        |                                                                                                                                                                                                                                                                                |

|--------------|---------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field           | Default | Access | Bit description                                                                                                                                                                                                                                                                |

| 7:0          | <i>curr2</i>        | 0x0     | RW     | <p>LED current for channel 2. Used for internal sensing.</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>currx</i> and <i>currx_target</i> shall be programmed to the same value.</p> |

| 15:8         | <i>curr2_target</i> | 0x0     | RW     | <p>Target LED current for channel 2</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>currx</i> and <i>currx_target</i> shall be programmed to the same value.</p>                      |

### 8.1.5 CURR3 register (Address 0x1A08)

Table 16: CURR3 register

| Addr: 0x1A08 |                     | CURR3   |        |                                                                                                                                                                                                                                                                                |

|--------------|---------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field           | Default | Access | Bit description                                                                                                                                                                                                                                                                |

| 7:0          | <i>curr3</i>        | 0x0     | RW     | <p>LED current for channel 3. Used for internal sensing.</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr3</i> and <i>curr3_target</i> shall be programmed to the same value.</p> |

| 15:8         | <i>curr3_target</i> | 0x0     | RW     | <p>Target LED current for channel 3</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr3</i> and <i>curr3_target</i> shall be programmed to the same value.</p>                      |

### 8.1.6 CURR4 register (Address 0x1A0A)

Table 17: CURR4 register (Write Access when system state == idle)

| Addr: 0x1A0A |                     | CURR4   |        |                                                                                                                                                                                                                                                                                |

|--------------|---------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field           | Default | Access | Bit description                                                                                                                                                                                                                                                                |

| 7:0          | <i>curr4</i>        | 0x0     | RW     | <p>LED current for channel 4. Used for internal sensing.</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>currx</i> and <i>currx_target</i> shall be programmed to the same value.</p> |

| 15:8         | <i>curr4_target</i> | 0x0     | RW     | <p>Target LED current for channel 4</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>currx</i> and <i>currx_target</i> shall be programmed to the same value.</p>                      |

### 8.1.7 CURR5 register (Address 0x1A0C)

Table 18: CURR5 register (Write Access when system state == idle)

| Addr: 0x1A0C |                     | CURR5   |        |                                                                                                                                                                                                                                                                                    |

|--------------|---------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit name            | Default | Access | Bit description                                                                                                                                                                                                                                                                    |

| 7:0          | <i>curr5</i>        | 0x0     | RW     | <p>LED current for channel 5. Used for internal sensing.</p> <p>00h: 0mA</p> <p>01h: 250µA</p> <p>02h: 500µA</p> <p>28h: 10mA</p> <p>50h: 20mA</p> <p>78h: 30mA</p> <p>FFh: 64mA</p> <p><b>Note:</b> Both fields currx and currx_target shall be programmed to the same value.</p> |

| 15:8         | <i>curr5_target</i> | 0x0     | RW     | <p>Target LED current for channel 5</p> <p>00h: 0mA</p> <p>01h: 250µA</p> <p>02h: 500µA</p> <p>28h: 10mA</p> <p>50h: 20mA</p> <p>78h: 30mA</p> <p>FFh: 64mA</p> <p><b>Note:</b> Both fields currx and currx_target shall be programmed to the same value.</p>                      |

### 8.1.8 CURR6 register (Address 0x1A0E)

Table 19: CURR6 register (Write Access when system state == idle)

| Addr: 0x1A0E |                     | CURR6   |        |                                                                                                                                                                                                                                                                                |

|--------------|---------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field           | Default | Access | Bit description                                                                                                                                                                                                                                                                |

| 7:0          | <i>curr6</i>        | 0x0     | RW     | <p>LED current for channel 6. Used for internal sensing.</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr6</i> and <i>curr6_target</i> shall be programmed to the same value.</p> |

| 15:8         | <i>curr6_target</i> | 0x0     | RW     | <p>Target LED current for channel 6</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr6</i> and <i>curr6_target</i> shall be programmed to the same value.</p>                      |

### 8.1.9 CURR7 register (Address 0x1A10)

Table 20: CURR7 register (Write Access when system state == idle)

| Addr: 0x1A10 |                     | CURR7   |        |                                                                                                                                                                                                                                                                                |

|--------------|---------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field           | Default | Access | Bit description                                                                                                                                                                                                                                                                |

| 7:0          | <i>curr7</i>        | 0x0     | RW     | <p>LED current for channel 7. Used for internal sensing.</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr7</i> and <i>curr7_target</i> shall be programmed to the same value.</p> |

| 15:8         | <i>curr7_target</i> | 0x0     | RW     | <p>Target LED current for channel 7</p> <p>00h: 0mA<br/>01h: 250µA<br/>02h: 500µA<br/>28h: 10mA<br/>50h: 20mA<br/>78h: 30mA<br/>FFh: 64mA</p> <p><b>Note:</b> Both fields <i>curr7</i> and <i>curr7_target</i> shall be programmed to the same value.</p>                      |

### 8.1.10 CURR\_LIM0 register (Address 0x1A12)

Table 21: CURR\_LIM0 register (Write Access when otp\_cust\_lock ==0)

| Addr: 0x1A12 |                  | CURR_LIM0 |        |                                                                                                                         |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                                         |

| 15:0         | <i>curr_lim0</i> | 0x0       | RW     | <p>LED current limits for channel 0</p> <p>Upper limit defined in bits [15:8]<br/>Lower limit defined in bits [7:0]</p> |

### 8.1.11 CURR\_LIM1 register (Address 0x1A14)

Table 22: CURR\_LIM1 register (Write Access when otp\_cust\_lock ==0)

| Addr: 0x1A14 |                  | CURR_LIM1 |        |                                                                                                             |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                             |

| 15:0         | <i>curr_lim1</i> | 0x0       | RW     | LED current limits for channel 1<br>Upper limit defined in bits [15:8]<br>Lower limit defined in bits [7:0] |

### 8.1.12 CURR\_LIM2 register (Address 0x1A16)

Table 23: CURR\_LIM2 register

| Addr: 0x1A16 |                  | CURR_LIM2 |        |                                                                                                             |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                             |

| 15:0         | <i>curr_lim2</i> | 0x0       | RW     | LED current limits for channel 2<br>Upper limit defined in bits [15:8]<br>Lower limit defined in bits [7:0] |

### 8.1.13 CURR\_LIM3 register (Address 0x1A18)

Table 24: CURR\_LIM3 register (Write Access when otp\_cust\_lock ==0)

| Addr: 0x1A18 |                  | CURR_LIM3 |        |                                                                                                             |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                             |

| 15:0         | <i>curr_lim3</i> | 0x0       | RW     | LED current limits for channel 3<br>Upper limit defined in bits [15:8]<br>Lower limit defined in bits [7:0] |

#### 8.1.14 CURR\_LIM4 register (Address 0x1A1A)

Table 25: CURR\_LIM4 register (Write Access when otp\_cust\_lock ==0)

| Addr: 0x1A1A |                  | CURR_LIM4 |        |                                                                                                             |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                             |

| 15:0         | <i>curr_lim4</i> | 0x0       | RW     | LED current limits for channel 4<br>Upper limit defined in bits [15:8]<br>Lower limit defined in bits [7:0] |

#### 8.1.15 CURR\_LIM5 register (Address 0x1A1C)

Table 26: CURR\_LIM5 register (Write Access when otp\_cust\_lock ==0)

| Addr: 0x1A1C |                  | CURR_LIM5 |        |                                                                                                             |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                             |

| 15:0         | <i>curr_lim5</i> | 0x0       | RW     | LED current limits for channel 5<br>Upper limit defined in bits [15:8]<br>Lower limit defined in bits [7:0] |

#### 8.1.16 CURR\_LIM6 register (Address 0x1A1E)

Table 27: CURR\_LIM6 register (Write Access when otp\_cust\_lock ==0)

| Addr: 0x1A1E |                  | CURR_LIM6 |        |                                                                                                             |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                             |

| 15:0         | <i>curr_lim6</i> | 0x0       | RW     | LED current limits for channel 6<br>Upper limit defined in bits [15:8]<br>Lower limit defined in bits [7:0] |

### 8.1.17 CURR\_LIM7 register (Address 0x1A20)

Table 28: CURR\_LIM7 register (Write Access when otp\_cust\_lock ==0)

| Addr: 0x1A20 |                  | CURR_LIM7 |        |                                                                                                             |

|--------------|------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit          | Bit field        | Default   | Access | Bit description                                                                                             |